Recently, insights from the upcoming GCC 14 compiler (GNU Compiler Collection), set to debut in the next few months, have partially revealed details about the AMD Zen 5 architecture. This sign indicates that the next-generation hardware products are approaching their official introduction more than ever before.Typically, when a new architecture is introduced, the chip manufacturer needs to provide additional information about it for compilers. This helps both operating systems and software developers understand the hardware better, allowing for more efficient utilization of the new products, often by supporting new instructions. Unlike Intel, which often updates the compiler before releasing new products, AMD usually waits until the product launch to update the compiler. However, with Zen 5, things seem to be different this time.

Recently, insights from the upcoming GCC 14 compiler (GNU Compiler Collection), set to debut in the next few months, have partially revealed details about the AMD Zen 5 architecture. This sign indicates that the next-generation hardware products are approaching their official introduction more than ever before.Typically, when a new architecture is introduced, the chip manufacturer needs to provide additional information about it for compilers. This helps both operating systems and software developers understand the hardware better, allowing for more efficient utilization of the new products, often by supporting new instructions. Unlike Intel, which often updates the compiler before releasing new products, AMD usually waits until the product launch to update the compiler. However, with Zen 5, things seem to be different this time. The anticipated completion of GCC 14 is scheduled for the upcoming March/April timeframe (half-yearly release cycle). At this point, application developers have received preliminary information to understand what to expect. The surprising revelation includes details about the Zen 5 (znver5) instruction set, as follows:AMD Family 1ah core-based CPUs with x86-64 instruction set support. (This encompasses BMI, BMI2, CLWB, F16C, FMA, FSGSBASE, AVX, AVX2, ADCX, RDSEED, MWAITX, SHA, CLZERO, AES, PCLMUL, CX16, MOVBE, MMX, SSE, SSE2, SSE3, SSE4A, SSSE3, SSE4.1, SSE4.2, ABM, XSAVEC, XSAVES, CLFLUSHOPT, POPCNT, RDPID, WBNOINVD, PKU, VPCLMULQDQ, VAES, AVX512F, AVX512DQ, AVX512IFMA, AVX512CD, AVX512BW, AVX512VL, AVX512BF16, AVX512VBMI, AVX512VBMI2, AVX512VNNI, AVX512BITALG, AVX512VPOPCNTDQ, GFNI, AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, PREFETCHI, and 64-bit instruction set extensions.)If we exclude what's already present in Zen 4, Zen 5 will introduce additional instructions including AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, and PREFETCHI. Notably, most of these instructions are already found in the latest Intel chips (Tiger Lake, Granite Rapids). Particularly, AVX-VNNI, a set of instructions supporting enhanced AI computations (VNNI), is a feature that Intel proudly boasts (absent in Zen 4). Therefore, it will be intriguing to observe the AI acceleration competition between Intel and AMD when Zen 5 is launched.

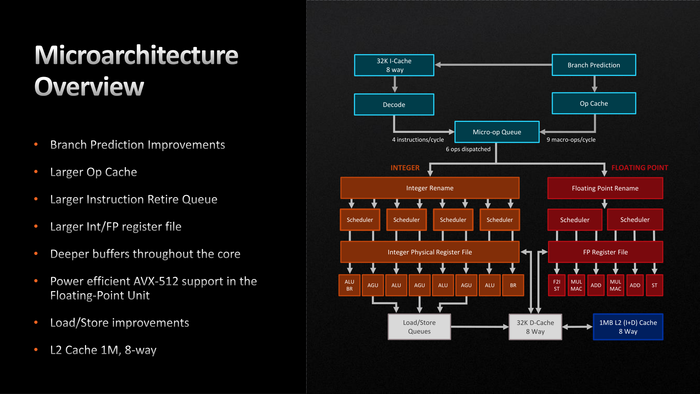

The anticipated completion of GCC 14 is scheduled for the upcoming March/April timeframe (half-yearly release cycle). At this point, application developers have received preliminary information to understand what to expect. The surprising revelation includes details about the Zen 5 (znver5) instruction set, as follows:AMD Family 1ah core-based CPUs with x86-64 instruction set support. (This encompasses BMI, BMI2, CLWB, F16C, FMA, FSGSBASE, AVX, AVX2, ADCX, RDSEED, MWAITX, SHA, CLZERO, AES, PCLMUL, CX16, MOVBE, MMX, SSE, SSE2, SSE3, SSE4A, SSSE3, SSE4.1, SSE4.2, ABM, XSAVEC, XSAVES, CLFLUSHOPT, POPCNT, RDPID, WBNOINVD, PKU, VPCLMULQDQ, VAES, AVX512F, AVX512DQ, AVX512IFMA, AVX512CD, AVX512BW, AVX512VL, AVX512BF16, AVX512VBMI, AVX512VBMI2, AVX512VNNI, AVX512BITALG, AVX512VPOPCNTDQ, GFNI, AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, PREFETCHI, and 64-bit instruction set extensions.)If we exclude what's already present in Zen 4, Zen 5 will introduce additional instructions including AVXVNNI, MOVDIRI, MOVDIR64B, AVX512VP2INTERSECT, and PREFETCHI. Notably, most of these instructions are already found in the latest Intel chips (Tiger Lake, Granite Rapids). Particularly, AVX-VNNI, a set of instructions supporting enhanced AI computations (VNNI), is a feature that Intel proudly boasts (absent in Zen 4). Therefore, it will be intriguing to observe the AI acceleration competition between Intel and AMD when Zen 5 is launched. Another intriguing detail is Zen 5's computational prowess. Each Zen 5 core boasts 6 ALUs (up from 4 in Zen 4), and AGUs are increased to 4 units (compared to 3 in Zen 4). The FP (floating-point) pipeline of Zen 5 is also twice the size of the previous architecture, enabling processing of a 512-bit operation in just 1 cycle (compared to 2 cycles in Zen 4). Operations like cmov/setcc can now run on any ALU, not limited to 2 specialized ALUs as in Zen 4. Additionally, Zen 5 and 5c instruction sets will be identical, similar to Zen 4 and 4c. This means software developers won't have to worry about compatibility issues if AMD introduces two different architectures simultaneously.With these new insights, 2024 promises to be a fascinating year for the PC landscape in particular and the tech market in general.Phoronix

Another intriguing detail is Zen 5's computational prowess. Each Zen 5 core boasts 6 ALUs (up from 4 in Zen 4), and AGUs are increased to 4 units (compared to 3 in Zen 4). The FP (floating-point) pipeline of Zen 5 is also twice the size of the previous architecture, enabling processing of a 512-bit operation in just 1 cycle (compared to 2 cycles in Zen 4). Operations like cmov/setcc can now run on any ALU, not limited to 2 specialized ALUs as in Zen 4. Additionally, Zen 5 and 5c instruction sets will be identical, similar to Zen 4 and 4c. This means software developers won't have to worry about compatibility issues if AMD introduces two different architectures simultaneously.With these new insights, 2024 promises to be a fascinating year for the PC landscape in particular and the tech market in general.Phoronix