Chip 14nm, chip 7nm, chip 5nm là những thuật ngữ quen thuộc mà chúng ta thường nghe. Tuy nhiên, ít khi nào ta dừng lại để suy ngẫm ý nghĩa thực sự của chúng. Trong bài viết này, tôi sẽ giải thích về chip 7nm hoặc 5nm để bạn hiểu rõ hơn về công nghệ mà laptop, desktop hoặc điện thoại của bạn đang sử dụng.

Chip 14nm, chip 7nm, chip 5nm là những thuật ngữ quen thuộc mà chúng ta thường nghe. Tuy nhiên, ít khi nào ta dừng lại để suy ngẫm ý nghĩa thực sự của chúng. Trong bài viết này, tôi sẽ giải thích về chip 7nm hoặc 5nm để bạn hiểu rõ hơn về công nghệ mà laptop, desktop hoặc điện thoại của bạn đang sử dụng.Hồi xưa

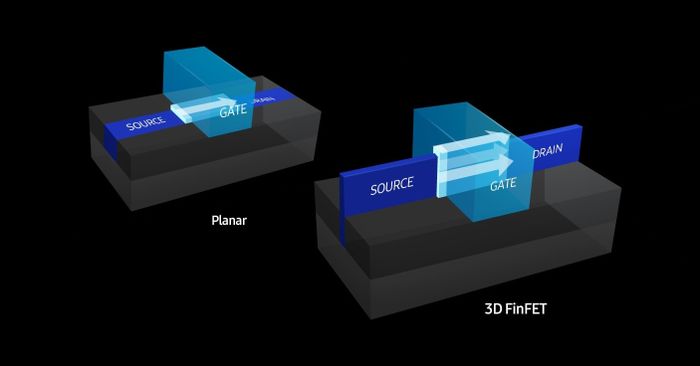

Hình ảnh dưới đây mô tả cấu trúc của một bóng bán dẫn (transistor) từ thời xưa, được trích từ trang web của Samsung. Loại transistor này được gọi là planar hoặc MOSFET, hay còn được biết đến là bóng bán dẫn dạng phẳng, và nó được sử dụng phổ biến trong các chip sản xuất trước từ 32nm trở xuống.

Các thành phần trong một transistor planar bao gồm:

- Cổng (G): là cực điều khiển, khi áp điện được áp vào, nó sẽ điều khiển dòng điện chảy giữa Nguồn và Dòng. Cực này được cách điện hoàn toàn với phần còn lại của bóng bán dẫn nhờ vào một lớp cách điện mỏng nhưng có độ cách điện cao (SiO2). Trong hình ảnh, nó được gọi là Cổng Oxide.

- Nguồn (S): là cực nguồn

- Dòng (D): là cực dòng, được sử dụng để nhận các hạt electron mang điện từ cực nguồn sang

- Cấu trúc dưới: là lớp chất nền

Với transistor planar truyền thống, khi nói về một con chip 32nm, số 32nm này đại diện cho khoảng cách giữa Nguồn và Dòng. Nó còn được gọi là chiều dài cổng. Đây cũng là kích thước nhỏ nhất mà dây chuyền sản xuất có thể tạo ra trong quá trình sản xuất. Khoảng cách càng ngắn, các electron di chuyển và tốn ít năng lượng hơn, tức là transistor hoạt động hiệu quả hơn. Điều này cũng đồng nghĩa với việc chip hoạt động hiệu quả hơn, tính toán nhanh và mạnh mẽ hơn.

Trong quá khứ, khi transistor vẫn ở dạng planar, con số 32nm cũng được sử dụng để đặt tên cho quy trình sản xuất ra con chip.

Chuyện ngày nay

Các nhà sản xuất chip luôn cố gắng tăng số lượng transistor trên con chip của họ để tăng hiệu suất xử lý. Điện thoại, laptop, thiết bị IoT, smartwatch… ngày càng nhỏ gọn, do đó việc tăng kích thước chip để tăng số transistor là không thể, vì vậy họ phải thu nhỏ transistor để tăng số lượng trên cùng một đơn vị diện tích.

Để thu nhỏ dây chuyền sản xuất xuống dưới mức 20nm, ngành công nghiệp chip phải đối mặt với thách thức lớn: làm thế nào để kiểm soát trạng thái On và Off một cách hiệu quả hơn và giảm thiểu rò rỉ điện tối đa.

Một công nghệ mới vừa ra đời, được gọi là FinFET, hãy nhìn vào hình bên trên. Không giống như bóng bán dẫn planar với cực source và cực drain nằm phẳng, các bóng bán dẫn FinFET sẽ tạo ra một cấu trúc 3 chiều. Cấu trúc này bao gồm việc tạo ra cực source và cực drain lên với hình dạng giống như một chiếc vây, và cực gate với lớp gate oxide sẽ bao quanh.

Lợi ích của điều này là gì?

Về mặt hiệu năng, trong bóng bán dẫn planar, electron chỉ di chuyển từ S → D trên một bề mặt duy nhất dưới cổng. Trong khi đó, trong bóng bán dẫn FinFET, electron sẽ di chuyển qua cả 3 bề mặt, cho phép nhiều electron được dịch chuyển hơn, từ đó FinFET có thể tạo ra hiệu năng tính toán cao hơn.

Chưa kể, khoảng cách gate length ngắn hơn cũng có nghĩa là electron tốn ít thời gian hơn để di chuyển, và transistor có thể chuyển đổi giữa trạng thái Bật và Tắt nhanh hơn, từ đó cũng giúp nâng cao hiệu năng.

Tóm lại, các con số nm có ý nghĩa gì ngày nay?

Trong thời điểm hiện tại, các dây chuyền sản xuất chip từ 14nm trở xuống đều sử dụng công nghệ FinFET. Dây chuyền 14nm, 10nm, 7nm của các nhà sản xuất như Intel, Samsung, TSMC và thậm chí cả 6nm sắp tới... tất cả đều đã chuyển sang sử dụng FinFET.

Tuy nhiên, số liệu 14nm, 10nm, 7nm... không còn đại diện cho chiều dài cổng nữa, bởi kiến trúc chip hiện nay đã được dựng lên theo hình dạng 3 chiều, không còn phẳng như transitor planar ngày trước nên không thể đo bằng chiều dài cổng nữa.

Ngày nay, các con số như 14nm, 10nm, 7nm... chỉ được dùng để chỉ 'thế hệ' dây chuyền sản xuất, còn gọi là process node, process technology, hoặc đơn giản là node. Các hãng sản xuất chip cũng không gọi chúng là kích thước bóng bán dẫn nữa, họ chỉ gọi là node. Qua từng node, kích thước bóng bán dẫn vẫn nhỏ dần do cải tiến dây chuyền, nhưng số liệu 7nm, 10nm không còn ám chỉ chiều dài cổng như trước kia.

Các con số 14nm, 10nm, 7nm... ngày nay chỉ mang ý nghĩa trong việc tiếp thị, giúp các hãng quảng bá rằng chip của họ ở 'thế hệ' nào. Số càng nhỏ thì người tiêu dùng càng nghĩ rằng nó càng cao cấp, và giúp các hãng cạnh tranh tốt hơn với đối thủ.

Tuy nhiên, các dây chuyền và công nghệ giữa các nhà sản xuất khác nhau, nên việc so sánh trực tiếp các con số cũng không hoàn toàn chính xác. Ví dụ, theo Wikichip:

- Mật độ bóng bán dẫn của chip Intel 10nm là 100,8 MTr/mm2

- Mật độ bóng bán dẫn trên chip TSMC 7nm là 96,49 MTr/mm2

- Mật độ bóng bán dẫn trên chip Samsung 7nm là 95,3 MTr/mm2

Như bạn có thể thấy, mặc dù chip 10nm của Intel có mật độ bóng bán dẫn cao hơn so với chip 7nm của Samsung và TSMC, nhưng sự chênh lệch không lớn. Do đó, tin đồn về chip Intel 10nm tương đương với chip 7nm của TSMC là vì lý do này.

Tuy nhiên, Intel vẫn đang gặp khó khăn trong việc cải tiến quy trình sản xuất của mình. Dây chuyền 10nm của họ đã gặp vấn đề vài lần về sản lượng và lỗi kĩ thuật. Cho đến năm 2020, dây chuyền 10nm của Intel mới bắt đầu ổn định. Trong khi đó, TSMC và Samsung vẫn thuận lợi trong việc nâng cấp dây chuyền bán dẫn của họ lên thế hệ mới.

Vậy làm sao mới đúng về hiệu năng?

Hiệu năng của một con chip phụ thuộc vào nhiều yếu tố: số lượng bóng bán dẫn, kiến trúc, tập lệnh, cách CPU giao tiếp với các thành phần khác trong hệ thống...

Cách đánh giá tạm thời nhất là chạy các bài kiểm tra hiệu năng để có số liệu cụ thể, và hiệu năng đó sẽ là của toàn bộ máy tính / thiết bị, chứ không chỉ của một con chip. Một con chip không thể tạo ra một mùa xuân.

Một phương pháp khác có thể là đo lượng phép tính dấu chấm động mà mỗi con chip có thể thực hiện trong một giây. Ví dụ, chip đồ họa của PlayStation 5 có thể thực hiện 10,3 TFLOPs (tỷ phép tính dấu chấm động mỗi giây), con chip của Xbox Series X là 12 TFLOPs, và GPU AMD Radeon Pro trong MacBook Pro 16' là 4 TFLOPs. Nhưng một lần nữa, gọi là chip nhưng để tạo ra số liệu này vẫn cần sự kết hợp của bộ nhớ, cache và nhiều yếu tố khác nữa, không chỉ riêng CPU.