Transistor phẳng là một dạng cơ bản của transistor MOSFET (phẳng 2D - planar) và là loại transistor phổ biến được sử dụng trước 14 nm.

Tại sao các nhà sản xuất bán dẫn chuyển sang FinFET và GAAFET thay vì sử dụng planar MOSFET?

Trở lại nguồn gốc của MOSFET - chúng là các FET hoặc transistor hiệu ứng trường. Với yêu cầu từ ngành bán dẫn, kích thước của các transistor ngày càng nhỏ. Điều này dẫn đến việc các thành phần của transistor (cổng, nguồn/drain, kênh) cũng phải thu nhỏ theo. Khi hiệu ứng trường không còn đủ mạnh, tác dụng làm thay đổi thuộc tính dẫn điện/ngắt điện của kênh lân cận không được đảm bảo - tương đương với chức năng của transistor không còn tin cậy.

Ngoài ra, transistor planar còn gặp tình trạng ngắn mạch nếu nhà sản xuất tăng hiệu ứng trường bằng cách tăng điện thế hoặc cường độ dòng điện trong mạch, đặc biệt là hiện tượng chui hầm lượng tử. Những yếu tố này làm cho việc thu nhỏ transistor planar trở nên vô nghĩa.

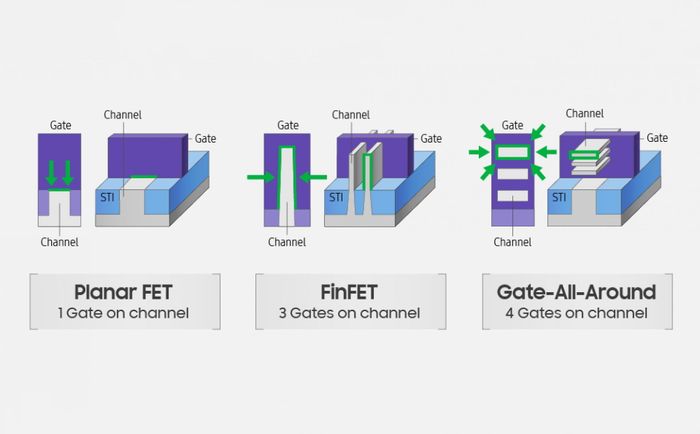

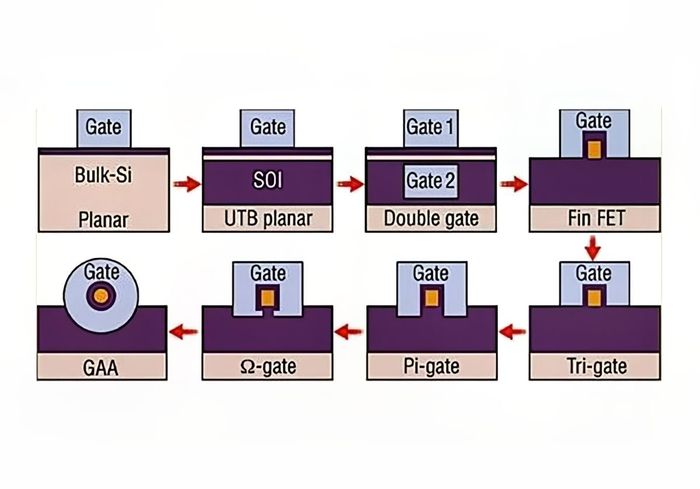

Video so sánh MOSFET planar, FinFET và GAAFET.Để giải quyết những thách thức nêu trên, ta có thể áp dụng một số phương án khác nhau. Ví dụ, sử dụng MOSFET hai cổng planar khi có một cổng bổ sung ở phía đối diện. Tuy ý tưởng này có hiệu quả gấp đôi nhờ hiệu ứng trường, nhưng thách thức trong việc sản xuất là cần phải ghép chồng hai wafer lên nhau và canh chỉnh hai cổng (có kích thước vài chục nm) sao cho đối xứng là rất khó khăn.Nếu việc đặt hai cổng ở 'trên & dưới' kênh quá phức tạp, tại sao chúng ta không đặt chúng ở hai bên 'trái & phải'? Đó là lý do tạo ra FinFET! Thay vì cổng 'nằm phẳng' lên nguồn/kênh/thu, bây giờ bộ ba này sẽ 'đâm ngang' qua cổng. Vì hình dạng của nguồn/kênh/thu lúc này mảnh như chiếc 'vảy cá' (fin), nên ta có tên gọi FinFET (FET hình vảy). Một biến thể khác của FinFET là Tri-Gate, trong đó transistor có nhiều fin hơn bình thường, mục đích là tăng hiệu quả của hiệu ứng trường. Mô tả sự 'tiến hóa' của cổng xung quanh bộ khuếch đạiTất nhiên, nếu đã có khả năng bao phủ cả 3 phía nguồn/kênh/thu thì tại sao chúng ta không làm điều đó đến tận cùng? Đó là lý do chúng ta đã phát triển những loại cổng mới như Pi-gate (hình chữ Pi), Omega-gate (hình chữ Omega) và Gate-all-around FET (cổng bọc toàn bộ kênh). Trong số đó, GAAFET (dây nano hoặc tấm nano hoặc RibbonFET hoặc MBCFET) là loại có hiệu ứng trường mạnh mẽ nhất. Một chi tiết cần lưu ý là GAAFET đã được đề xuất trước cả FinFET, nhưng chưa được thương mại hóa cho đến bây giờ. Lý do là gì?Hiệu suất so với chi phí kinh tếCó một sự thật rằng các thiết kế transistor đa cổng không mới. Chúng đã được phát triển từ những năm cuối thập kỷ 80 hoặc đầu thập kỷ 90 của thế kỷ trước. Tuy nhiên, chúng mới được thương mại hóa sau vài thập kỷ. Lý do là gì?

Mô tả sự 'tiến hóa' của cổng xung quanh bộ khuếch đạiTất nhiên, nếu đã có khả năng bao phủ cả 3 phía nguồn/kênh/thu thì tại sao chúng ta không làm điều đó đến tận cùng? Đó là lý do chúng ta đã phát triển những loại cổng mới như Pi-gate (hình chữ Pi), Omega-gate (hình chữ Omega) và Gate-all-around FET (cổng bọc toàn bộ kênh). Trong số đó, GAAFET (dây nano hoặc tấm nano hoặc RibbonFET hoặc MBCFET) là loại có hiệu ứng trường mạnh mẽ nhất. Một chi tiết cần lưu ý là GAAFET đã được đề xuất trước cả FinFET, nhưng chưa được thương mại hóa cho đến bây giờ. Lý do là gì?Hiệu suất so với chi phí kinh tếCó một sự thật rằng các thiết kế transistor đa cổng không mới. Chúng đã được phát triển từ những năm cuối thập kỷ 80 hoặc đầu thập kỷ 90 của thế kỷ trước. Tuy nhiên, chúng mới được thương mại hóa sau vài thập kỷ. Lý do là gì?Trên lý thuyết, mọi hình thái transistor có thể được sản xuất ở bất kỳ tiến trình nào, bao gồm cả 180 nm, 45 nm, 14 nm và 7 nm. Tuy nhiên, có những hình thái 'dễ' và 'khó' hơn để tạo ra. So với việc xây dựng căn nhà, việc sản xuất transistor cũng tương tự - từ việc đóng cọc, làm móng, làm hầm, làm nền cho đến việc xây tường, đổ tấm và làm mái. Với transistor phức tạp hơn, quá trình sản xuất cũng sẽ phức tạp và mất nhiều thời gian hơn.

Nếu so sánh với transistor dạng planar, trong FinFET, phần nguồn/kênh/thu 'đứng' lên và xuyên qua cổng. Điều này tạo ra sự khác biệt rõ rệt trong quá trình cấy ion và ăn mòn vi mạch. Với GAAFET, sự phức tạp càng tăng khi phần sheet (nguồn/kênh/thu) chìm hoàn toàn bên trong cổng. Hơn nữa, không chỉ có một sheet mà có nhiều sheet song song xen kẽ với cổng. Quá trình sản xuất giống như việc xây dựng một căn nhà cao tầng, mỗi tầng phải hoàn thiện điện nước và nội thất trước khi tiến hành tầng tiếp theo. Cả hai còn đặt ra yêu cầu chính xác tuyệt đối trên quy mô hàng triệu ~ hàng tỷ transistor đơn lẻ.

Video miêu tả quá trình sản xuất transistor FinFET, cho thấy có nhiều công đoạn hơn so với video trước đó.

Với các đặc tính đã nêu, dễ nhận thấy rằng nếu không có nhu cầu thực sự, các nhà sản xuất bán dẫn sẽ không áp dụng các thiết kế transistor phức tạp trừ khi không còn sự lựa chọn nào khác. Intel chẳng hạn, đã bắt đầu áp dụng FinFET từ tiến trình 22 nm, trong khi TSMC và các nhà sản xuất khác chỉ áp dụng từ 14/16 nm trở lên. Lý do chủ yếu là do các chip của Intel thường có xung nhịp cao (trên 3 GHz), trong khi khách hàng của TSMC thì không đặt ra yêu cầu cao như vậy nên vẫn có thể sử dụng thiết kế planar.

Đối với GAAFET, Samsung là nhà sản xuất đầu tiên áp dụng từ tiến trình 3 nm (3GAP, 2023). TSMC chỉ triển khai GAAFET từ 2 nm trở lên (N2, 2024). Còn Intel cho biết sẽ áp dụng ngay ở node Intel 20A. Tuy nhiên, con số nm hiện nay chỉ còn mang tính 'tham khảo' (marketing) vì chúng chỉ có ý nghĩa trên thiết kế planar. Kể từ khi thiết kế FinFET được ra đời, nm chỉ còn là biểu tượng cho mật độ transistor cao/thấp hơn so với các tiến trình khác. Khi sang GAAFET, để biết xem tiến trình của hãng nào 'tốt hơn', chúng ta cần xem xét chi tiết 'cấu hình' từng bên thay vì chỉ dựa vào con số marketing. Năm 2024 hứa hẹn là một năm rất thú vị đối với ngành công nghệ bán dẫn.

Sau GAAFET, điều gì sẽ xảy ra tiếp theo?

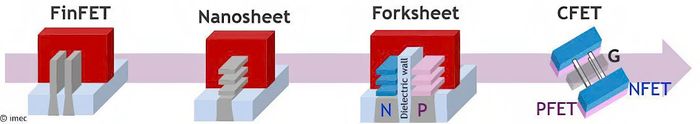

2 ý tưởng mới về thiết kế transistor: Forksheet và CFET.

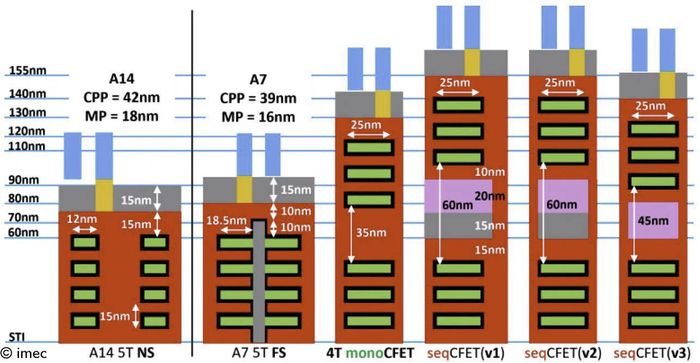

2 ý tưởng mới về thiết kế transistor: Forksheet và CFET. So sánh các đặc tính kỹ thuật của GAA, FS và CFET. Nguồn: IMECTrong hướng đầu tiên, IMEC đề xuất hai ý tưởng mới: Forksheet (FS) và CFET (complementary FET). Cả hai đều dựa trên ý tưởng kết hợp transistor loại N và P lại thành một. Thực tế, transistor N và P hiện nay vẫn được sản xuất độc lập, điều này có nghĩa là một tổ hợp N-P sẽ cần hai transistor độc lập. Nếu có thể kết hợp cả hai thành một transistor, không gian chiếm dụng sẽ giảm đi đáng kể. Tuy nhiên, điểm trừ của thiết kế này là không phải lúc nào các nhà sản xuất cũng cần một transistor tổ hợp như vậy. Và hiệu suất làm việc của transistor này có thể không hiệu quả bằng hai transistor độc lập. Vì vậy, việc áp dụng FS hoặc CFET có thực tế hay không vẫn là một câu hỏi chưa có câu trả lời.Với hướng thứ hai, các nhà sản xuất đã từng sử dụng các phương pháp này trong quá khứ. Chẳng hạn như việc sử dụng silic đẩy (strained silicon) để làm cho electron di chuyển dễ dàng hơn, hoặc sử dụng vật liệu cách điện High-K để thay thế silic dioxide (SiO2), hoặc sử dụng silic trên cách điện (SOI) để giảm điện dung ký sinh của transistor.

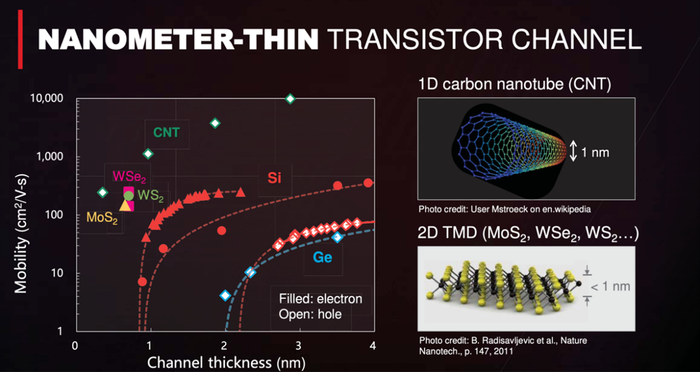

So sánh các đặc tính kỹ thuật của GAA, FS và CFET. Nguồn: IMECTrong hướng đầu tiên, IMEC đề xuất hai ý tưởng mới: Forksheet (FS) và CFET (complementary FET). Cả hai đều dựa trên ý tưởng kết hợp transistor loại N và P lại thành một. Thực tế, transistor N và P hiện nay vẫn được sản xuất độc lập, điều này có nghĩa là một tổ hợp N-P sẽ cần hai transistor độc lập. Nếu có thể kết hợp cả hai thành một transistor, không gian chiếm dụng sẽ giảm đi đáng kể. Tuy nhiên, điểm trừ của thiết kế này là không phải lúc nào các nhà sản xuất cũng cần một transistor tổ hợp như vậy. Và hiệu suất làm việc của transistor này có thể không hiệu quả bằng hai transistor độc lập. Vì vậy, việc áp dụng FS hoặc CFET có thực tế hay không vẫn là một câu hỏi chưa có câu trả lời.Với hướng thứ hai, các nhà sản xuất đã từng sử dụng các phương pháp này trong quá khứ. Chẳng hạn như việc sử dụng silic đẩy (strained silicon) để làm cho electron di chuyển dễ dàng hơn, hoặc sử dụng vật liệu cách điện High-K để thay thế silic dioxide (SiO2), hoặc sử dụng silic trên cách điện (SOI) để giảm điện dung ký sinh của transistor. So sánh khả năng dẫn điện giữa silic, germani và một số vật liệu 2D.Các vật liệu 2D bao gồm graphene (mạng lưới carbon dạng tổ ong), Molybdenum Disulfide (MoS2), Tungsten Disulfide (WS2), Tungsten Diselenide (WSe2)... CNT (ống carbon) mặc dù không phải là 2D nhưng cũng có thuộc tính điện lý phù hợp để làm bán dẫn (đường kính tối thiểu 1 nm). Hầu hết các vật liệu này cho phép dòng electron chảy qua mạng tinh thể tốt hơn ngay cả khi độ dày < 1 nm (germani thua ở 2 nm và silic thua ở 1 nm).

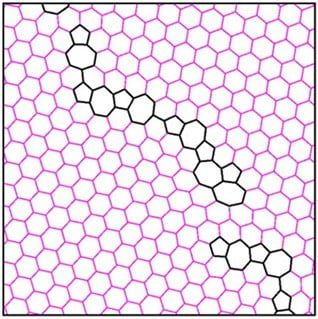

So sánh khả năng dẫn điện giữa silic, germani và một số vật liệu 2D.Các vật liệu 2D bao gồm graphene (mạng lưới carbon dạng tổ ong), Molybdenum Disulfide (MoS2), Tungsten Disulfide (WS2), Tungsten Diselenide (WSe2)... CNT (ống carbon) mặc dù không phải là 2D nhưng cũng có thuộc tính điện lý phù hợp để làm bán dẫn (đường kính tối thiểu 1 nm). Hầu hết các vật liệu này cho phép dòng electron chảy qua mạng tinh thể tốt hơn ngay cả khi độ dày < 1 nm (germani thua ở 2 nm và silic thua ở 1 nm). Vấn đề xuất hiện khi 'nuôi' graphene bằng phương pháp CVD.Mặc dù vật liệu 2D rất hấp dẫn, quá trình sản xuất và tích hợp chúng lên các wafer silic không hề đơn giản. Bề dày của một lớp vật liệu trong các tiến trình MOSFET thường có hàng trăm đến hàng ngàn phân tử (một nguyên tử silic có đường kính chỉ 0.2 nm). Tạo ra một lớp vật liệu mỏng chỉ vài lớp phân tử là rất khó khăn. Ngoài ra, rủi ro lỗi trên mạng tinh thể là rất lớn. Ví dụ, graphene, vật liệu 2D 'trưởng thành' nhất, vẫn gặp phải tình trạng 'sạn' (grain) khi sản xuất bằng phương pháp CVD. Phương pháp mới như ALD cũng đang được nghiên cứu, nhưng chưa có đủ dữ liệu để so sánh.Một khó khăn khác khi sản xuất vật liệu 2D là chúng thường được tạo ra ở nhiệt độ cực cao (> 600 °C) trên các tấm đồng hoặc sapphire thay vì trực tiếp trên wafer silic. Điều này tạo ra vấn đề về việc chuyển giao lớp phân tử 2D từ các tấm khác sang wafer silic.

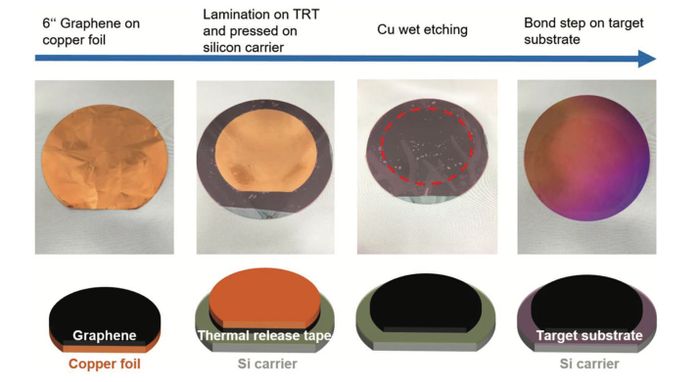

Vấn đề xuất hiện khi 'nuôi' graphene bằng phương pháp CVD.Mặc dù vật liệu 2D rất hấp dẫn, quá trình sản xuất và tích hợp chúng lên các wafer silic không hề đơn giản. Bề dày của một lớp vật liệu trong các tiến trình MOSFET thường có hàng trăm đến hàng ngàn phân tử (một nguyên tử silic có đường kính chỉ 0.2 nm). Tạo ra một lớp vật liệu mỏng chỉ vài lớp phân tử là rất khó khăn. Ngoài ra, rủi ro lỗi trên mạng tinh thể là rất lớn. Ví dụ, graphene, vật liệu 2D 'trưởng thành' nhất, vẫn gặp phải tình trạng 'sạn' (grain) khi sản xuất bằng phương pháp CVD. Phương pháp mới như ALD cũng đang được nghiên cứu, nhưng chưa có đủ dữ liệu để so sánh.Một khó khăn khác khi sản xuất vật liệu 2D là chúng thường được tạo ra ở nhiệt độ cực cao (> 600 °C) trên các tấm đồng hoặc sapphire thay vì trực tiếp trên wafer silic. Điều này tạo ra vấn đề về việc chuyển giao lớp phân tử 2D từ các tấm khác sang wafer silic. Quá trình chuyển giao lớp graphene từ tấm đồng sang wafer silic là một thách thức lớn.Tổng quan, những đường mới vẫn còn đầy khó khăn và thách thức. Một số có thể không bao giờ trở thành hiện thực. Tuy nhiên, transistor sẽ tiếp tục thu nhỏ và các chip sẽ có nhiều transistor hơn trong những năm tới. Điều quan trọng là liệu chi phí sản xuất chip có tăng lên khi công nghệ sản xuất trở nên phức tạp hơn không?

Quá trình chuyển giao lớp graphene từ tấm đồng sang wafer silic là một thách thức lớn.Tổng quan, những đường mới vẫn còn đầy khó khăn và thách thức. Một số có thể không bao giờ trở thành hiện thực. Tuy nhiên, transistor sẽ tiếp tục thu nhỏ và các chip sẽ có nhiều transistor hơn trong những năm tới. Điều quan trọng là liệu chi phí sản xuất chip có tăng lên khi công nghệ sản xuất trở nên phức tạp hơn không?