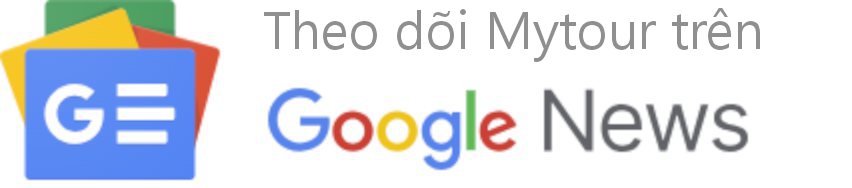

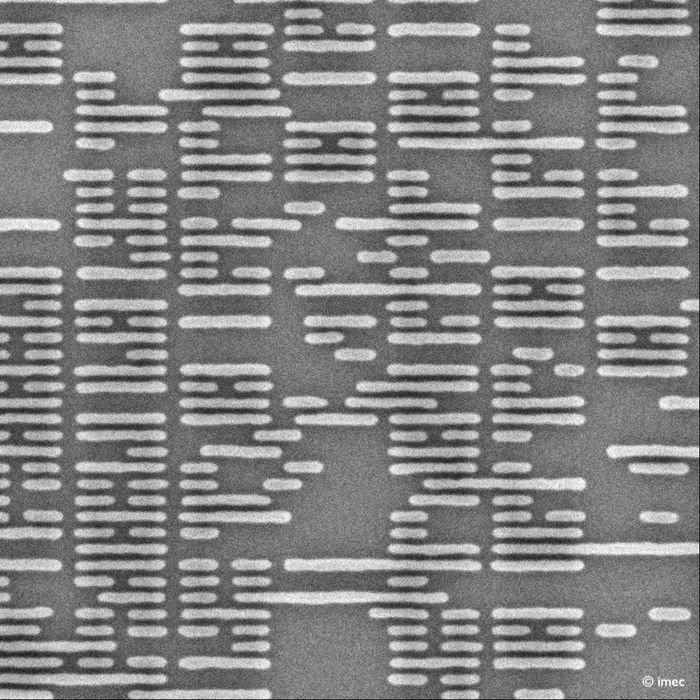

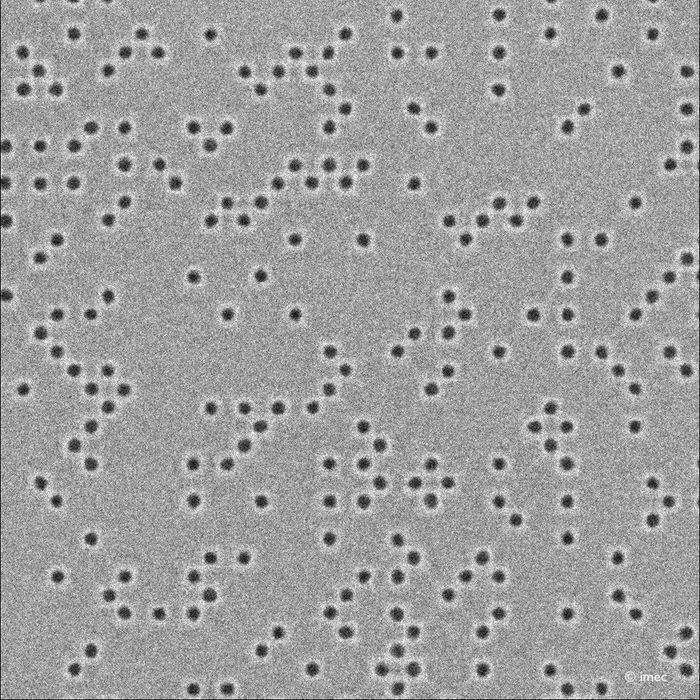

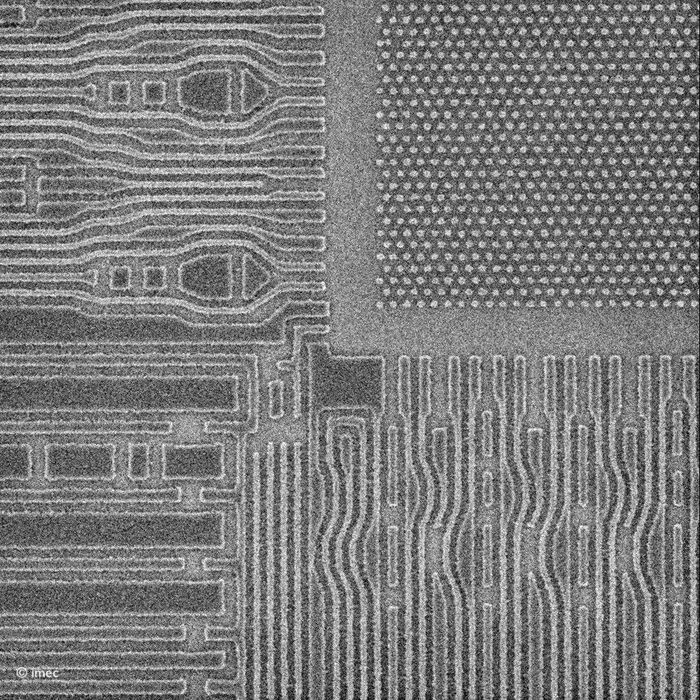

IMEC - đối tác chiến lược quan trọng của ASML trong việc phát triển công nghệ EUV High-NA (0.55) - vừa công bố hình ảnh về các cấu trúc bán dẫn được sản xuất bằng nền tảng litho mới nhất. Mặc dù ASML (Hà Lan) là một tên tuổi nổi bật trong ngành bán dẫn hiện nay, họ không đơn độc trong cuộc đua EUV mà còn dựa vào nhiều đối tác khác để cùng nghiên cứu. Một trong số đó là IMEC (Bỉ), đồng hành cùng ASML từ những ngày đầu phát triển công nghệ 0.55 NA EUV. Gần đây, IMEC công bố các kết quả sơ bộ từ hệ thống TWINSCAN EXE:5000 (đang cung cấp cho Intel và Samsung) cho thấy khả năng của nền tảng litho mới. Cụ thể, chỉ sau một lần phơi sáng, hệ thống EUV 0.55 NA đã tạo ra các mạch logic với bề dày kim loại 9.5 nm và khoảng cách pitch 19 nm, đạt cự ly giữa hai đầu (tip-to-tip) dưới 20 nm. Cấu trúc xuyên lỗ (vias) ngẫu nhiên với khoảng cách giữa các tâm 30 nm cũng cho thấy độ rõ nét và sự đồng nhất tuyệt vời. Các chi tiết 2D ở khoảng cách P22 nm cũng thể hiện hiệu suất vượt trội, cho thấy tiềm năng ứng dụng công nghệ High-NA trong việc thiết kế mạch 2D.

IMEC - đối tác chiến lược quan trọng của ASML trong việc phát triển công nghệ EUV High-NA (0.55) - vừa công bố hình ảnh về các cấu trúc bán dẫn được sản xuất bằng nền tảng litho mới nhất. Mặc dù ASML (Hà Lan) là một tên tuổi nổi bật trong ngành bán dẫn hiện nay, họ không đơn độc trong cuộc đua EUV mà còn dựa vào nhiều đối tác khác để cùng nghiên cứu. Một trong số đó là IMEC (Bỉ), đồng hành cùng ASML từ những ngày đầu phát triển công nghệ 0.55 NA EUV. Gần đây, IMEC công bố các kết quả sơ bộ từ hệ thống TWINSCAN EXE:5000 (đang cung cấp cho Intel và Samsung) cho thấy khả năng của nền tảng litho mới. Cụ thể, chỉ sau một lần phơi sáng, hệ thống EUV 0.55 NA đã tạo ra các mạch logic với bề dày kim loại 9.5 nm và khoảng cách pitch 19 nm, đạt cự ly giữa hai đầu (tip-to-tip) dưới 20 nm. Cấu trúc xuyên lỗ (vias) ngẫu nhiên với khoảng cách giữa các tâm 30 nm cũng cho thấy độ rõ nét và sự đồng nhất tuyệt vời. Các chi tiết 2D ở khoảng cách P22 nm cũng thể hiện hiệu suất vượt trội, cho thấy tiềm năng ứng dụng công nghệ High-NA trong việc thiết kế mạch 2D.

Cấu trúc mạch logic với bề dày kim loại 9.5 nm và khoảng cách 19 nm

Cấu trúc xuyên lỗ (vias) ngẫu nhiên với khoảng cách giữa các tâm 30 nm

Cấu trúc 2D với khoảng cách P22 nm

Cấu trúc kết hợp node landing pad và đường bit line của DRAM

Ngoài khả năng in mạch logic, IMEC còn thử nghiệm in mẫu DRAM bằng công nghệ High-NA. Kết quả cho thấy chỉ sau một lần phơi sáng, đã tích hợp thành công phần thiết kế node landing pad với đường bit line của DRAM ở khoảng cách P32 nm. Tiến bộ này cho thấy có thể loại bỏ việc phơi sáng nhiều lần để tạo ra các chi tiết bộ nhớ chỉ với một lần phơi sáng High-NA. Những phát hiện này là nền tảng quan trọng để xây dựng “hệ sinh thái” High-NA EUV, không chỉ cho IMEC và ASML mà còn cho nhiều đối tác bán dẫn khác. Chỉ khi hệ thống litho 0.55 NA thể hiện chất lượng vượt trội hơn 0.33 NA, các công ty sản xuất chip như TSMC, UMC, hay Samsung mới cân nhắc đầu tư. Hiện tại, Intel là công ty duy nhất sở hữu hệ thống High-NA EUV đầu tiên trên thế giới, ngoài ASML.