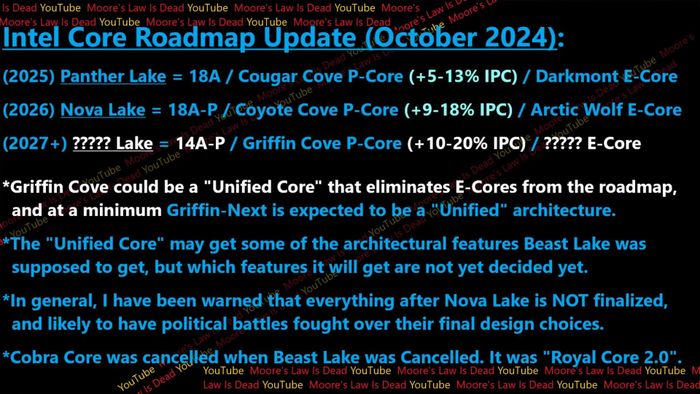

Dựa trên thông tin từ MLID (Moore's Law Is Dead), Intel sẽ ngừng phát triển E-core theo hình thức hiện tại và chuyển hướng tương tự như AMD với Zen 5/5c. Điều này có thể sẽ diễn ra vào năm 2027, khi thế hệ P-core Griffin Cove ra mắt.MLID cho biết trong 3 năm tới, Intel sẽ giới thiệu 3 thế hệ P-core khác nhau: Cougar Cove (dùng cho Panther Lake), Coyote Cove (dành cho Nova Lake), và Griffin Cove (sản phẩm cụ thể chưa rõ). Đồng thời, Intel cũng duy trì 2 thế hệ E-core là Darkmont và Arctic Wolf cho các mẫu Lake tương ứng. Đặc biệt, Arctic Wolf sẽ không theo truyền thống -mont như các thế hệ E-core trước (Tremont, Gracemont, Crestmont, Skymont), báo hiệu một sự thay đổi lớn đối với kiến trúc tiết kiệm năng lượng này.

Dựa trên thông tin từ MLID (Moore's Law Is Dead), Intel sẽ ngừng phát triển E-core theo hình thức hiện tại và chuyển hướng tương tự như AMD với Zen 5/5c. Điều này có thể sẽ diễn ra vào năm 2027, khi thế hệ P-core Griffin Cove ra mắt.MLID cho biết trong 3 năm tới, Intel sẽ giới thiệu 3 thế hệ P-core khác nhau: Cougar Cove (dùng cho Panther Lake), Coyote Cove (dành cho Nova Lake), và Griffin Cove (sản phẩm cụ thể chưa rõ). Đồng thời, Intel cũng duy trì 2 thế hệ E-core là Darkmont và Arctic Wolf cho các mẫu Lake tương ứng. Đặc biệt, Arctic Wolf sẽ không theo truyền thống -mont như các thế hệ E-core trước (Tremont, Gracemont, Crestmont, Skymont), báo hiệu một sự thay đổi lớn đối với kiến trúc tiết kiệm năng lượng này. Theo MLID, Intel sẽ ngừng sử dụng E-core từ năm 2027

Theo MLID, Intel sẽ ngừng sử dụng E-core từ năm 2027Với thế hệ Griffin Cove, Intel sẽ không phân chia P-core và E-core mà thay vào đó sẽ sử dụng một thiết kế chung gọi là "Unified Core". Đây là phương pháp tương tự như cách AMD triển khai Zen 4 và Zen 5, sau đó tối ưu hóa một số yếu tố để tạo ra các nhân nhỏ gọn Zen 4c và 5c. Hệ số IPC của Zen 4c/5c gần như không khác biệt so với Zen 4/5 (khi cùng xung nhịp), và chúng vẫn chia sẻ các tập lệnh ISA, vì vậy việc chuyển luồng tính toán giữa các nhân sẽ không gặp vấn đề. Hiện tại, với kiến trúc Hybrid của Intel, P-core và E-core có cấu trúc khác nhau, trong đó E-core thiếu bộ ISA đầy đủ như P-core, dẫn đến khả năng gặp sự cố hoặc lỗi ứng dụng khi chuyển dữ liệu giữa hai loại nhân này. Hiệu năng của E-core cũng thấp hơn khá nhiều so với P-core, và thực tế, ít người dùng hài lòng với kiến trúc hybrid hiện tại.

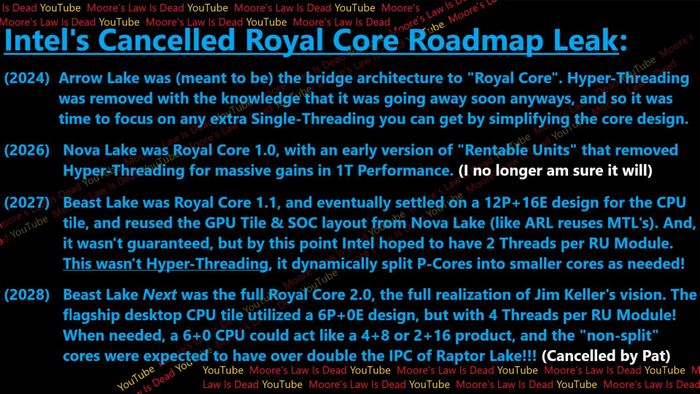

Dự án Royal Core của Jim Keller có thể đã bị Pat Gelsinger hủy bỏ

Dự án Royal Core của Jim Keller có thể đã bị Pat Gelsinger hủy bỏMLID còn tiết lộ thêm một câu chuyện thú vị về dự án chip do Jim Keller phát triển (trước khi rời Intel). Jim từng đứng đầu dự án Royal Core, một thiết kế cho phép một nhân P-core có thể "biến thành" nhiều nhân nhỏ hơn khi cần thiết. Nova Lake được cho là tiền thân của dự án này. Tuy nhiên, do Jim Keller đã rời đi khá sớm, độ chính xác của thông tin này vẫn chưa rõ ràng. Điều chúng ta biết là kiến trúc Hybrid với P-core và E-core đã xuất hiện khi Jim và Raja gia nhập Intel. Nếu Pat Gelsinger thực sự quyết định loại bỏ E-core như thông tin đã đề cập, có lẽ đã có nhiều biến động nội bộ tại Intel.