Sau nhiều năm bị lãng quên và để các đối thủ vượt mặt, gã khổng lồ x86 đang dần trở lại với Lunar Lake, đánh dấu bước khởi đầu quan trọng. Năm 2024 có vẻ là thời điểm quan trọng trên thị trường vi xử lý toàn cầu, khi các đại diện ARM như Apple và Qualcomm đang chiếm ưu thế. AMD mặc dù có phần khả quan hơn Intel, nhưng cuộc cạnh tranh giữa các kiến trúc x86 và ARM vẫn là một bài toán khó cho các CEO ngành chip. Chip Lunar Lake (LNL) chỉ là một phần trong bức tranh dài hạn.

Sau nhiều năm bị lãng quên và để các đối thủ vượt mặt, gã khổng lồ x86 đang dần trở lại với Lunar Lake, đánh dấu bước khởi đầu quan trọng. Năm 2024 có vẻ là thời điểm quan trọng trên thị trường vi xử lý toàn cầu, khi các đại diện ARM như Apple và Qualcomm đang chiếm ưu thế. AMD mặc dù có phần khả quan hơn Intel, nhưng cuộc cạnh tranh giữa các kiến trúc x86 và ARM vẫn là một bài toán khó cho các CEO ngành chip. Chip Lunar Lake (LNL) chỉ là một phần trong bức tranh dài hạn.Tổng quan về thị trường vi xử lý qua các năm

Trước năm 2015, chúng ta thường phân loại x86 và ARM thành hai nhóm chính: máy tính (khổ lớn) và thiết bị di động (cầm tay) hoặc thiết bị nhúng. Xu hướng này dẫn đến việc suy nghĩ rằng x86 chỉ phù hợp cho những ai cần hiệu suất cao, trong khi ARM chỉ dành cho việc tiết kiệm điện. Mặc dù tư duy này không hoàn toàn sai, nhưng nó cho thấy sự hiểu biết chưa đầy đủ về bản chất của x86 và ARM.

Intel Atom đã từng được sử dụng trên smartphone Android cách đây nhiều năm, nhưng vì phải chạy giả lập nên hiệu suất rất thấp.

Intel Atom đã từng được sử dụng trên smartphone Android cách đây nhiều năm, nhưng vì phải chạy giả lập nên hiệu suất rất thấp.

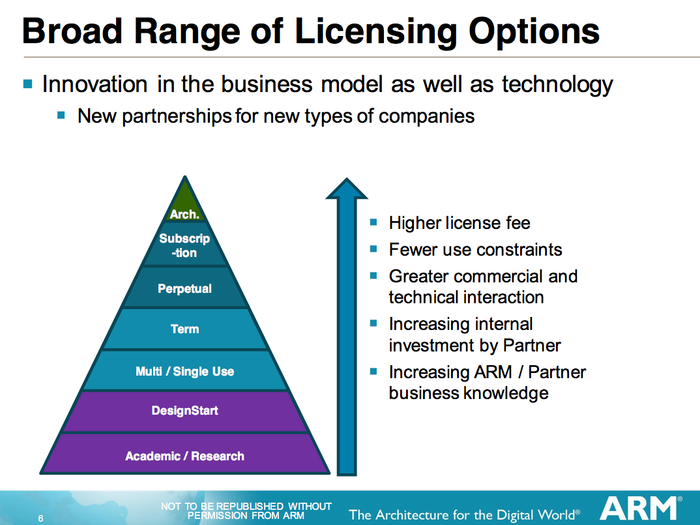

Cơ chế cấp phép bản quyền kiến trúc của ARM khác biệt hoàn toàn so với việc đóng kín kiến trúc x86 của Intel

Trong khi ARM, với nhiều nhà phát triển nhờ vào cơ chế cấp phép bản quyền, ngày càng cải thiện qua từng năm, thì x86, với chỉ hai đại diện chính là Intel và AMD (VIA có thể bỏ qua), dường như không có nhiều thay đổi, đặc biệt là Intel. Trước đây, tôi đã phân tích lý do tại sao Intel lại như vậy trong một bài viết trước. Có thể tóm gọn trong một câu - lãnh đạo kém! Vì khi người đứng đầu không đủ khả năng, sản phẩm khó có thể tiến bộ. Tuy nhiên, tình hình đã bắt đầu thay đổi từ khi Pat Gelsinger trở thành CEO của Intel (tương tự như tình hình của AMD trước khi Lisa Su trở thành CEO). Chúng ta có thể thấy sự thay đổi rõ ràng từ Ice Lake (ICL) đến Meteor Lake (MTL) và hiện tại là LNL. Dĩ nhiên, LNL không phải là điểm kết thúc, vẫn còn Arrow Lake (ARL) và Panther Lake trong tương lai.

Những bước tiến của x86 (CISC) và ARM (RISC)

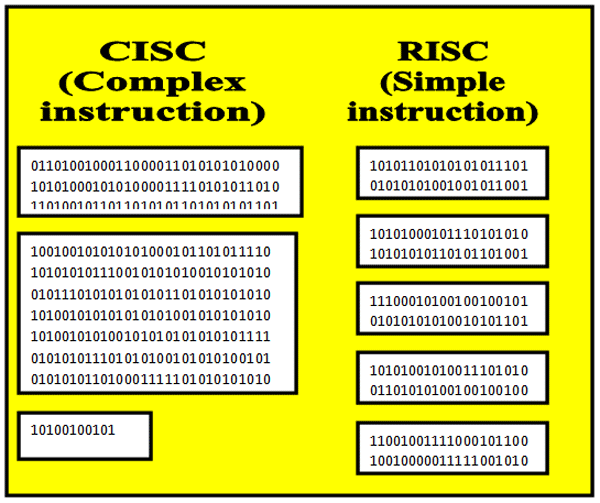

Có thể bạn thắc mắc - điều gì tạo nên sức mạnh của một con chip? Chắc chắn là silicon! Các con chip mạnh mẽ nhất hiện nay chứa hàng chục, thậm chí hàng trăm tỷ transistor. Tuy nhiên, đây chỉ là cách nhìn bề ngoài. Silicon giống như số vốn bạn có, nhưng việc làm thế nào để tận dụng số vốn đó một cách hiệu quả và an toàn phụ thuộc vào nhiều yếu tố khác. Đối với chip, yếu tố quan trọng chính là kiến trúc của nó. Hiện có nhiều loại mô hình kiến trúc khác nhau, nhưng chủ yếu là RISC và CISC.

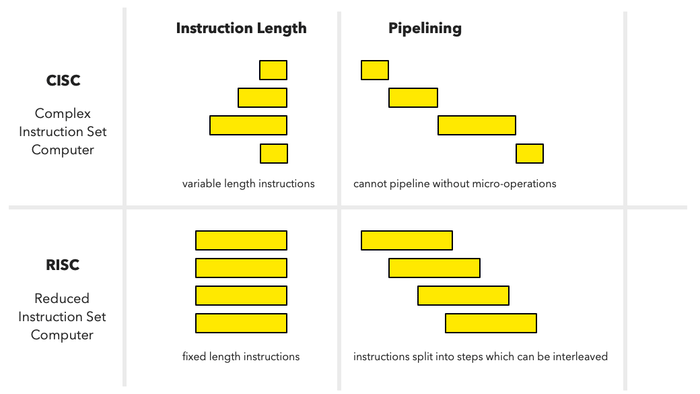

Điểm khác biệt chính giữa CISC và RISC là độ dài của các tập lệnh

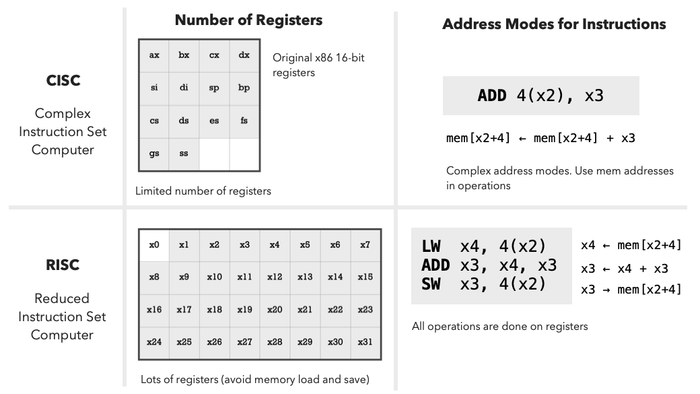

Tuy RISC và CISC là một chủ đề khá rộng, tôi sẽ chỉ nêu những khác biệt chính và các yếu tố dẫn đến kiến trúc LNL hiện tại. RISC là kiến trúc chip với các tập lệnh có cấu trúc đơn giản và cố định, thường chỉ được thực hiện trong các ALU/FPU và không truy cập vào bộ nhớ ngoài, mà chỉ xử lý trên các thanh ghi. RISC có các lệnh riêng để lấy dữ liệu từ bên ngoài vào, nên còn được gọi là kiến trúc xuất-nhập (load-store).

Ngược lại, CISC sử dụng các tập lệnh phức tạp hơn, thường có khả năng truy cập dữ liệu ngoài các thanh ghi (như cache hoặc DRAM). Mục tiêu là thực hiện nhiều phép toán với một tập lệnh duy nhất (trong khi một tập lệnh RISC thường chỉ thực hiện một phép toán). Vì vậy, các tập lệnh CISC có độ dài không cố định, làm cho thiết kế và mở rộng ống lệnh CISC phức tạp hơn so với RISC.

Thiết kế ống lệnh trong CISC phức tạp hơn so với RISC

Tuy nhiên, điều đó không có nghĩa là RISC luôn đơn giản. Khi chiều dài của các thanh ghi gia tăng, các tập lệnh cũng cần được mở rộng. Để xử lý nhiều công việc hơn, RISC cũng cần có nhiều tập lệnh hơn. Bên cạnh đó, vì các tập lệnh có độ dài cố định (trong một thế hệ kiến trúc), việc chuyển đổi sang thế hệ mới đòi hỏi phải bổ sung cơ chế để xử lý các tập lệnh cũ. Ngược lại, CISC không gặp vấn đề này vì với độ dài tập lệnh biến động, các tập lệnh cũ vẫn hoạt động bình thường trên kiến trúc mới.

RISC cần thực hiện nhiều tập lệnh hơn để hoàn thành một công việc

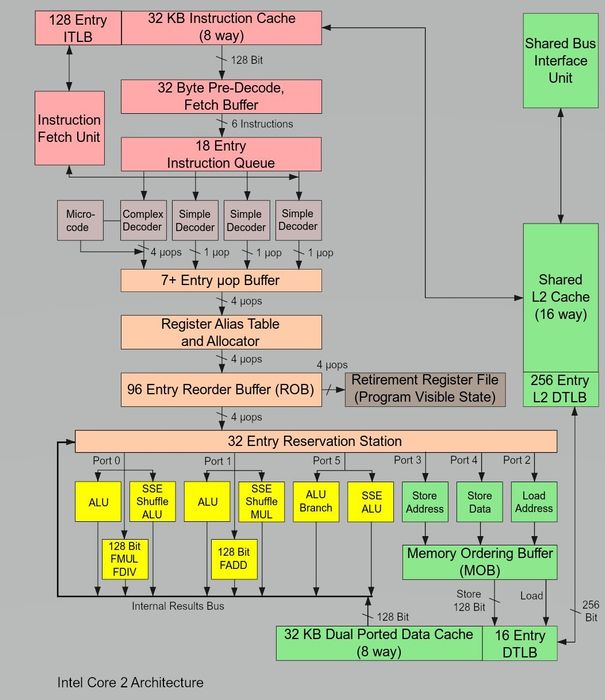

Số lượng decoder của mỗi hãng không phải là chỉ số so sánh giữa các hãng, mà là để đánh giá sự thay đổi trong nội bộ của hãng đó. Ví dụ, các kiến trúc K7/K8/K10 của AMD đều sử dụng decoder 3-wide, trong khi các kiến trúc Zen 1/2/3/4 sử dụng decoder 4-wide. Tuy nhiên, sự khác biệt về IPC giữa các kiến trúc là đáng kể. Đối với Intel, từ thế hệ Core đầu tiên đến Skylake (Core đời 6-10) đều sử dụng decoder 4-wide, trong khi đời 11 (Cypress Cove) có decoder 5-wide. Decoder 6-wide xuất hiện từ đời 12 và tiếp tục cho đến nay. Còn với LNL?

Decoder 8-wide.

Tăng tốc nhanh chóng

Kích thước của decoder chỉ là một phần nhỏ trong cấu trúc tổng thể của chip. Mặc dù không phải là chỉ số tuyệt đối để đo sức mạnh (IPC), nó phản ánh 'tiềm năng' mà con chip có thể đạt được. Một cách hình dung đơn giản về kiến trúc chip là so sánh với một doanh nghiệp sản xuất, trong đó mỗi nhân xử lý giống như một nhà máy. Decoder đóng vai trò như bộ phận tiếp nhận đơn hàng từ ban giám đốc hoặc đối tác, phân tích và chia nhỏ công việc cho các phân xưởng hoặc dây chuyền sản xuất. Một decoder lớn hơn có thể xử lý và phân chia đơn hàng một cách hiệu quả hơn.

Kiến trúc Intel Core (2006) với decoder 4-wide

Một quy tắc cơ bản là không thể tuyển quá nhiều trưởng phòng kinh doanh mà chỉ có một trưởng phòng sản xuất. Cần có sự cân bằng giữa bộ phận phân chia công việc và bộ phận xử lý công việc. Trên thực tế, decoder thường ít hơn so với các bộ phận khác. Như đã nêu, AMD đã duy trì decoder 3-wide trong nhiều năm trước khi chuyển sang 4-wide. Intel cũng tương tự. Tuy nhiên, với thế hệ LNL mới (cụ thể là P-core Lion Cove), thay vì phát triển decoder 6-wide như trên Redwood Cove (MTL), Intel đã nhảy vọt lên 8-wide. Tại sao lại cần phải làm nhanh như vậy?

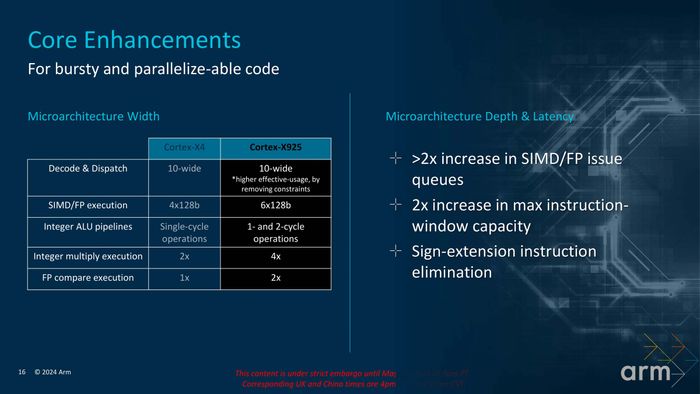

Kiến trúc ARM Cortex-X925 (2024) với decoder 10-wide

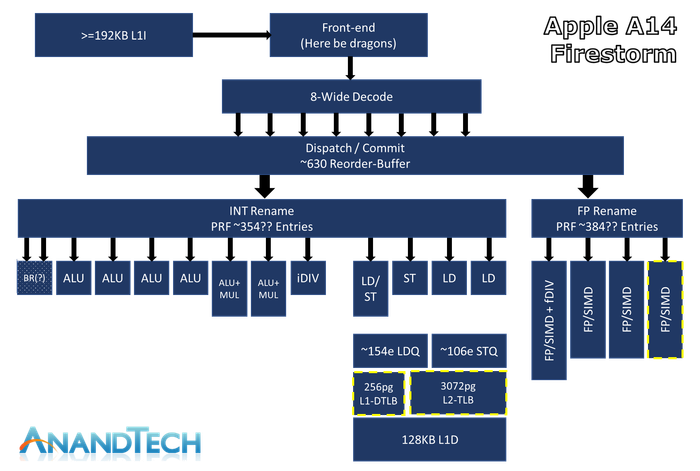

Apple đã triển khai decoder 8-wide từ năm 2020 (theo ảnh Anandtech)

Với việc ARM đã nâng cấp lên decoder 8/10-wide, gần đây ARM đã giới thiệu nhân Cortex-X925, được coi là bản nâng cấp từ Cortex-X4 ra mắt năm 2023, cả hai đều sử dụng decoder 10-wide. Dù decoder của x86 và ARM có sự khác biệt, việc duy trì số lượng decoder thấp sẽ gây khó khăn trong việc cạnh tranh với đối thủ. Do đó, Intel đã quyết định 'nhảy cóc' lên thẳng 8-wide để không bị tụt lại. Theo dự đoán của mình, Lion Cove sẽ là nền tảng cho kiến trúc x86 của Intel trong nhiều năm tới, vì thay đổi số lượng decoder gần như tương đương với việc giới thiệu một kiến trúc hoàn toàn mới, và một kiến trúc thường tồn tại khoảng 4-5 năm.