Kể từ khi Intel triển khai kiến trúc nhân lai, Thread Director (TD) đã trở thành yếu tố then chốt, giúp phân phối công việc giữa các lõi xử lý để tối ưu hóa hiệu suất cho hệ điều hành và ứng dụng. Với dòng vi xử lý Lunar Lake (LNL), Thread Director đã được tinh chỉnh để phù hợp với thế hệ CPU này, bao gồm việc loại bỏ Hyper Threading. Bên cạnh đó, sự phát triển của AI đã làm cho việc trang bị NPU4 trở nên cần thiết.

Kể từ khi Intel triển khai kiến trúc nhân lai, Thread Director (TD) đã trở thành yếu tố then chốt, giúp phân phối công việc giữa các lõi xử lý để tối ưu hóa hiệu suất cho hệ điều hành và ứng dụng. Với dòng vi xử lý Lunar Lake (LNL), Thread Director đã được tinh chỉnh để phù hợp với thế hệ CPU này, bao gồm việc loại bỏ Hyper Threading. Bên cạnh đó, sự phát triển của AI đã làm cho việc trang bị NPU4 trở nên cần thiết.Cơ chế Thread Director mới - 8 lõi có giống như 4 lõi không?

Trong bài viết trước, chúng ta đã biết rằng LNL (hay chính xác hơn là Lion Cove) sẽ không hỗ trợ SMT. Intel cho rằng một nhân P-core được tối ưu hóa sẽ xử lý công việc hiệu quả hơn khi không có SMT. Tuy nhiên, theo quan điểm của tôi, nguyên nhân chính không phải là SMT mà là vấn đề nằm ở TD.

Có phải cơ chế TD trên Raptor Lake là nguyên nhân gây crash?

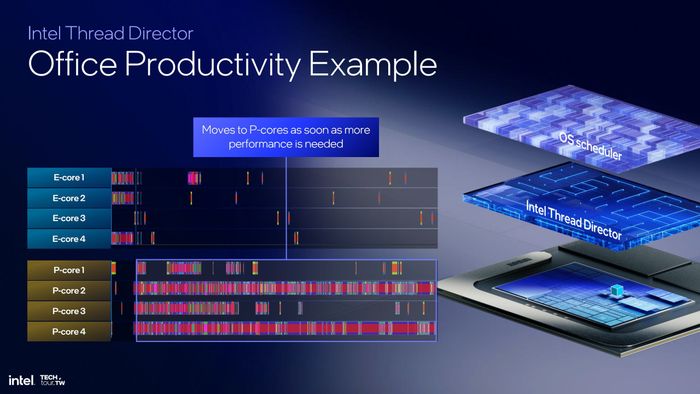

TD hoạt động như cầu nối giữa hệ điều hành và vi xử lý, phân tích yêu cầu ứng dụng để quyết định xem nên dùng E-core hay P-core cho công việc nào đó. Tuy nhiên, TD cũng là nguyên nhân gây ra sự rối rắm. Bạn có thể đã nghe về tình trạng crash trên các máy tính sử dụng Core đời 13/14? Dù có nhiều lý do được đưa ra, theo tôi, vấn đề chính là do TD liên tục chuyển luồng công việc giữa E-Core và P-core, khiến hệ điều hành và ứng dụng không thể theo kịp dữ liệu, dẫn đến tình trạng crash trong những trường hợp xấu nhất.

Cách TD phân loại công việc

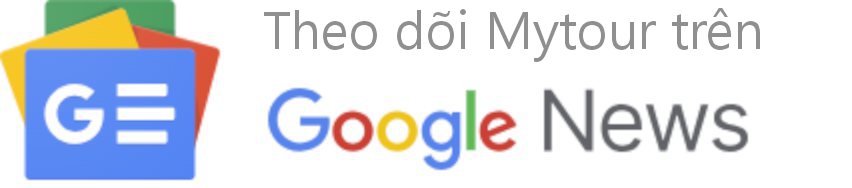

Với dòng vi xử lý MTL, Intel đã thay đổi cách TD hoạt động. Thay vì phân phối luồng công việc một cách ngẫu nhiên, E-core sẽ được ưu tiên xử lý trước, chỉ khi nhu cầu tính toán tăng cao thì công việc mới được chuyển cho P-core (không có chiều ngược lại). Phương pháp này lý thuyết sẽ tránh được tình trạng công việc bị phân phối không đồng nhất như trước. Tuy nhiên, MTL hiện chỉ có trên laptop, nên chúng ta chưa có cơ hội kiểm chứng mọi tình huống.

Tiếp theo, với LNL, Intel lại có thêm sự thay đổi!

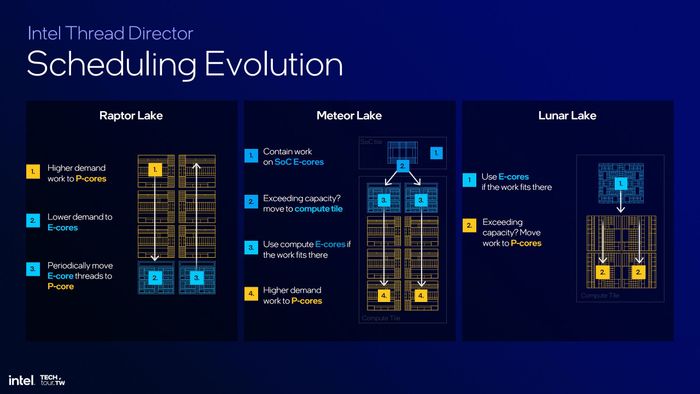

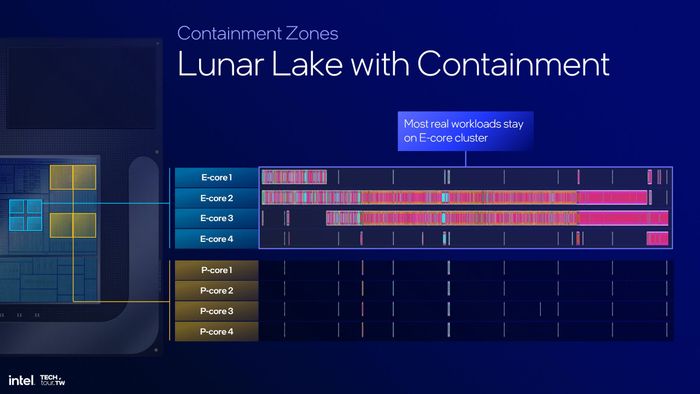

Nhìn tổng quan, TD của LNL hoạt động tương tự như MTL - ưu tiên E-core trước khi chuyển sang P-core. Tuy nhiên, khi xem xét chi tiết, quá trình luân chuyển công việc lại tương đương với 1 E-core = 1 P-core, đây là điểm mấu chốt. Ở các thế hệ trước MTL, P-core hỗ trợ SMT xử lý 2 luồng, trong khi E-core chỉ xử lý 1 luồng. Vậy với 8 E-core hoặc 8 luồng và 6 P-core hoặc 12 luồng, việc phân phối sẽ như thế nào? Rõ ràng, P-core sẽ nhận 2 luồng từ E-core trong khi một số P-core chỉ nhận 1 luồng, dẫn đến việc phân chia công việc không hiệu quả.

4 luồng E-core sẽ có 4 luồng P-core hỗ trợ khi cần thiết

Trong trường hợp chỉ thực hiện công việc nhẹ, chỉ có 4/8 nhân hoạt động

Theo cách hoạt động này, nếu máy tính chỉ thực hiện một công việc nặng, thì gần như chỉ có 4 P-core hoạt động. Khi máy ở trạng thái nhàn rỗi, cũng chỉ có 4 E-core làm việc. Để khai thác toàn bộ 8 nhân, cần phải có cả công việc nặng lẫn nhẹ hoặc nhiều nhiệm vụ vừa phải. Vì vậy, về cơ bản, LNL hoạt động giống như một CPU 4(+) nhân hơn là 8 nhân. Đây là cách nhìn cá nhân, bạn có thể có quan điểm khác.

NPU4 - Đủ sức mạnh cho Copilot+ PC

Mười năm trước, nếu ai nhắc đến AI cá nhân, chắc hẳn nhiều người sẽ cười vì dữ liệu lúc đó còn phân tán và thuật toán chưa phát triển, đưa lên PC chẳng có ý nghĩa thực tiễn. Nhưng giờ đây, năm 2024, mọi thứ đã thay đổi. AI đã hiện diện khắp nơi và AI cá nhân đang dần trở thành tiêu chuẩn chung. Các hãng như AMD, Intel và Qualcomm đều tích hợp AI vào quảng cáo sản phẩm của mình. Tuy nhiên, cả MTL và Ryzen Mobile 7000/8000 vẫn chưa đủ 'mạnh' theo yêu cầu của Microsoft.

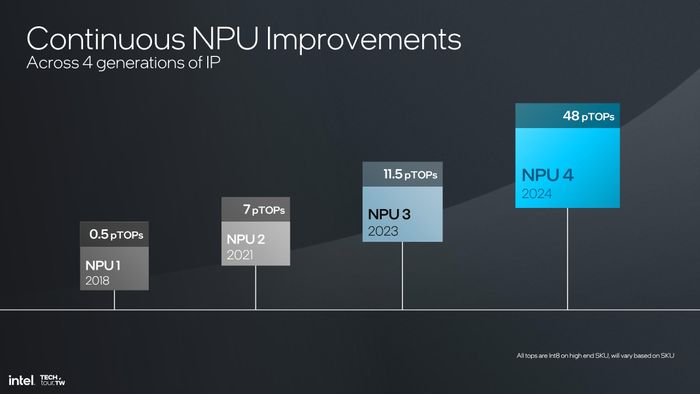

Quá trình phát triển NPU của Intel

So sánh giữa NPU3 và NPU4

Vì NPU1 và NPU2 chưa được công bố, nên chúng ta sẽ không đề cập đến chúng. NPU4 trên LNL hiện tại là phiên bản kế thừa từ NPU3 trên MTL. Cấu trúc cơ bản của NPU4 vẫn giống như NPU3, nhưng với số lượng đơn vị chức năng nhiều hơn. Từ 2 khối NCE (Neural Compute Engine), giờ đây chúng ta có 6 khối. Và nhìn tổng thể, khối NPU4 trông khá quen thuộc.

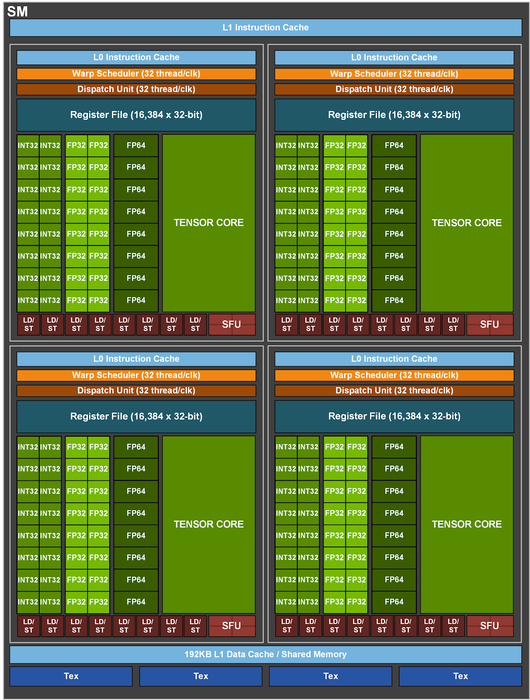

Sơ đồ khối SM trên GPU NVIDIA A100

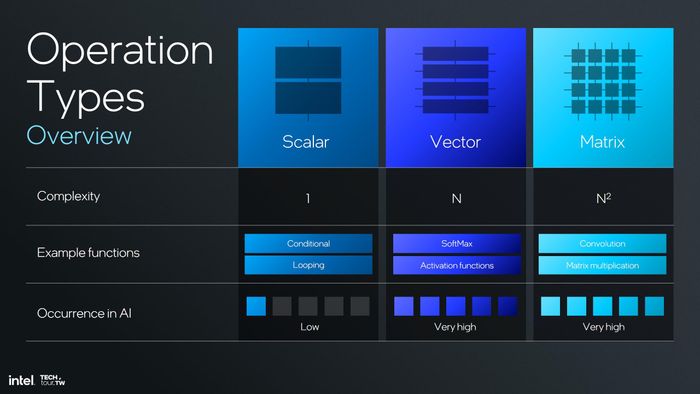

Đúng vậy, cấu trúc của NPU4 từ Intel có nhiều điểm tương đồng với GPU NVIDIA, với các khối NCE tương đương các khối SM trên GPU. Điều này không quá bất ngờ vì cấu trúc GPU thường dựa trên SIMD để xử lý vector. Sự xuất hiện của AI đã thúc đẩy sự phát triển các khối MAC (nhân/chồng dữ liệu) để xử lý ma trận. Sự bổ sung các mảng MAC có thể coi là một bước tiến từ SIMD. CPU thường xử lý các phép toán vô hướng (scalar) kém hiệu quả với AI, trong khi GPU xử lý vector và mạng neuron là ma trận. NVIDIA đã thêm các nhân Tensor, và Intel đã tích hợp bộ mở rộng XMX cho GPU Xe để giải quyết vấn đề ma trận này. Vì vậy, không có gì ngạc nhiên khi GPU của LNL có khả năng AI lên tới 67 TOPS, vượt qua cả NPU4.

GPU là cỗ máy xử lý vector, nâng cấp nhân ma trận dễ hơn so với CPU

Tuy nhiên, GPU chủ yếu phục vụ cho xử lý đồ họa. Trừ khi nhu cầu xử lý hình ảnh 2D/3D của bạn là rất thấp, GPU mới có thể hoàn toàn tập trung vào AI. Nếu bạn yêu cầu GPU vừa chơi game vừa xử lý AI, điều này có thể tạo ra áp lực lớn. Do đó, việc có một khối ASIC chuyên dụng cho AI vẫn là lựa chọn tốt hơn.

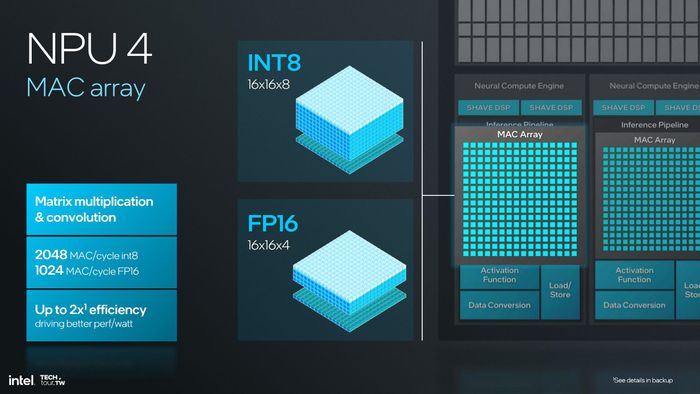

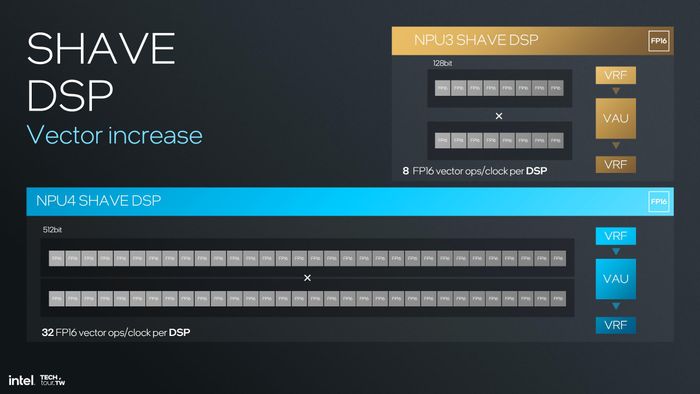

Bên trong mỗi NCE, có hai thành phần chính: SHAVE DSP để xử lý toán vector và Inference Pipeline dành cho nhân ma trận. SHAVE DSP trên NPU4 có kích thước lớn gấp 4 lần so với thế hệ trước, với thanh ghi tăng từ 128-bit lên 512-bit, cho phép xử lý 32 vector FP16 mỗi chu kỳ (trước đây là 8 vector). Inference Pipeline vẫn giữ nguyên như trước, với mỗi mảng MAC có hiệu suất 2048 phép toán INT8 mỗi chu kỳ hoặc 1024 phép toán FP16 mỗi chu kỳ.

Cấu trúc mảng MAC trên NPU4 vẫn giữ nguyên như trên NPU3

SHAVE DSP trên NPU4 mạnh mẽ hơn gấp nhiều lần so với thế hệ trước

So sánh hiệu suất AI giữa NPU3 và NPU4

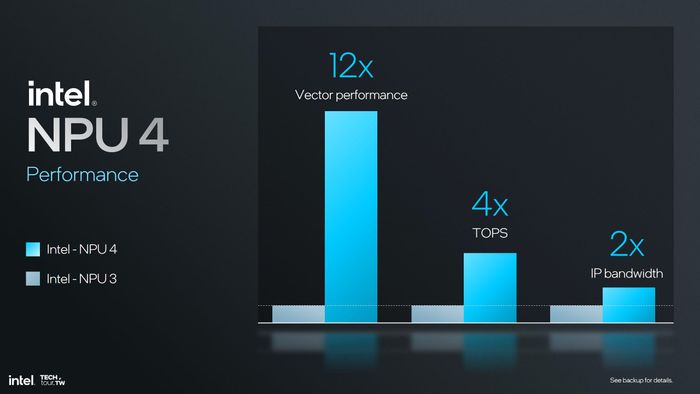

Theo đánh giá chung, Intel cho biết NPU4 vượt trội với hiệu suất tính toán vector cao gấp 12 lần so với NPU3 (do SHAVE DSP được nâng cấp đáng kể), hiệu suất TOPS tăng gấp 4 lần và băng thông dữ liệu cũng được cải thiện gấp đôi.

Khi gã khổng lồ thức tỉnh

Rõ ràng, Intel đã trải qua một thời gian dài 'ngủ quên' khi ra mắt các dòng chip Core mới mỗi năm nhưng hiệu suất gần như không thay đổi. Đây là giai đoạn dưới sự lãnh đạo của Brian Krzanich, người cũng đã do dự trong việc đầu tư vào công nghệ EUV, khiến các kỹ sư Intel phải vật lộn với tiến trình 14 nm. Dòng chip Cannon Lake, dự kiến phát triển trên dây chuyền 10 nm, cuối cùng đã bị hủy bỏ. Kiến trúc Sunny Cove, vốn được coi là bước tiến lớn nhất kể từ kiến trúc Core (2006, 65 nm), cũng không thể thực hiện vì dây chuyền 10 nm chưa sẵn sàng. Nó buộc phải quay lại 14 nm với tên gọi Cypress Cove.

LNL được sản xuất trên dây chuyền TSMC N3B

Chỉ khi Pat Gelsinger đảm nhận vị trí CEO, Intel mới bắt đầu giải quyết các vấn đề tồn đọng, bao gồm việc thuê TSMC để sản xuất nếu dây chuyền nội bộ không đáp ứng được. MTL và LNL là những ví dụ rõ ràng (ARL có lẽ cũng vậy). LNL được chế tạo bằng tiến trình N3B mới nhất, và sẽ là đối thủ đáng gờm cho các sản phẩm của AMD và Qualcomm.

Việc 'nhảy cóc' lên 8-wide decoder chứng tỏ Pat sẵn sàng thực hiện những thay đổi cần thiết để cạnh tranh. Nếu các tin đồn về hiệu năng của LNL là chính xác, thì đó là lý do hợp lý cho các cải tiến trên Lion Cove. Đây sẽ là nền tảng cho Intel trong ít nhất 3 năm tới trong lĩnh vực PC. Vấn đề còn lại là phiên bản desktop (ARL) sẽ có bao nhiêu nhân Lion Cove và sức mạnh của nó sẽ ra sao khi không còn bị giới hạn TDP như trên LNL?

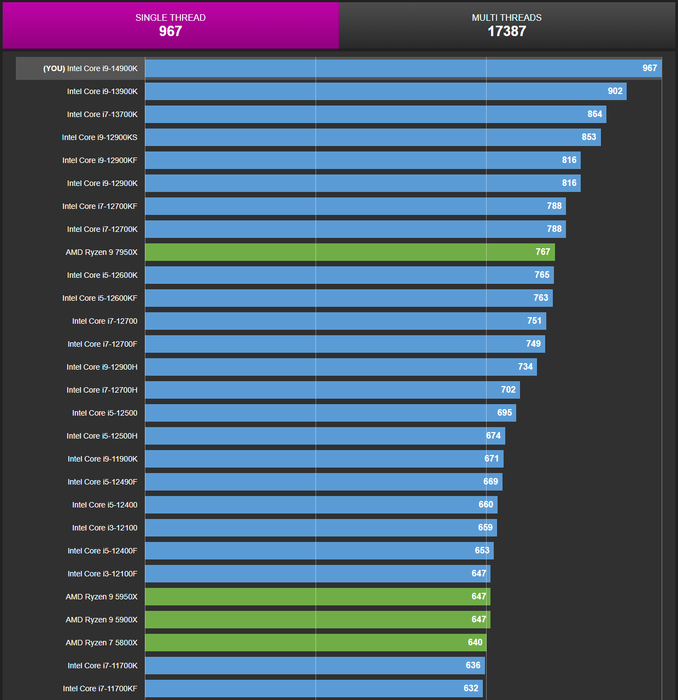

Hiệu năng đơn luồng của Raptor Lake vẫn vượt trội hơn Zen 4

Điểm đáng chú ý nhất về Skymont đối với mình là hiệu suất khi đi kèm với LLC/Ringbus. Do LNL là thiết kế tiết kiệm điện, chúng ta sẽ không thấy được điều này. Nhưng còn ARL thì sao? Liệu Intel có sử dụng chung LLC như Lion Cove cho ARL không? Cần lưu ý rằng các chip Core 13/14 hiện tại vẫn đứng đầu về hiệu năng đơn luồng, nhờ vào Raptor Cove.

Về NPU, hiện tại chúng ta chưa có nhiều thông tin về khối ASIC này, vì AI cá nhân vẫn còn là một tính năng mới. Phải mất thời gian dài để đánh giá hiệu quả của NPU từ các công ty khác nhau. Tuy nhiên, cá nhân mình nghĩ rằng phần lớn NPU sẽ chỉ đáp ứng tiêu chuẩn Copilot+ mà không được nâng cấp quá mạnh, vì hiệu năng CPU/GPU vẫn là yếu tố quan trọng nhất.