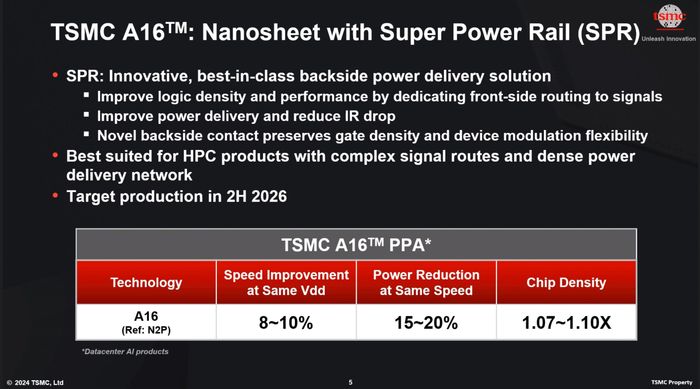

Với công nghệ mạng phân phối điện ở phía sau (backside power delivery network hoặc BSPDN), A16 đứng là một trong những quá trình sản xuất chip có độ phức tạp cao nhất mà công ty gia công Đài Loan từng giới thiệu.

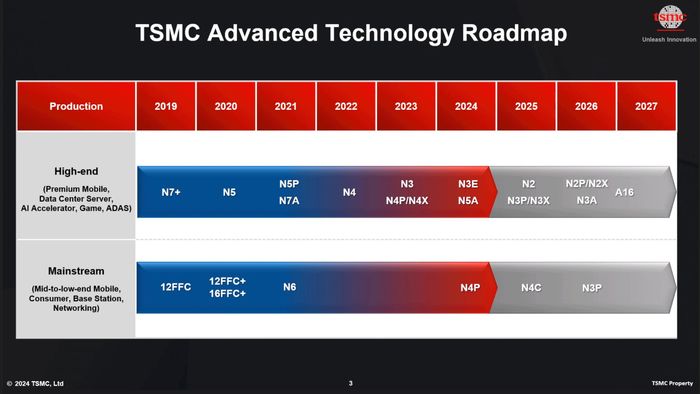

Với công nghệ mạng phân phối điện ở phía sau (backside power delivery network hoặc BSPDN), A16 đứng là một trong những quá trình sản xuất chip có độ phức tạp cao nhất mà công ty gia công Đài Loan từng giới thiệu.Một trong những trọng điểm công nghệ chính trong năm 2024 của TSMC là việc 'đẩy' BSPDN từ tiến trình N2 (theo kế hoạch ban đầu) sang A16. Động thái này cho thấy bước ngoặt quan trọng trong việc áp dụng các công nghệ mới đi vào sản xuất hàng loạt. Dự kiến node N2 sẽ được áp dụng từ 2025 còn A16 sẽ có mặt vào cuối 2026.

Lộ Trình Sản Xuất Bán Dẫn Của TSMC Đến Năm 2027

Nhưng BSPDN là gì và tại sao TSMC lại phải trì hoãn việc áp dụng nó ở thế hệ N2/N2P/N2X?

BSPDN là gì?

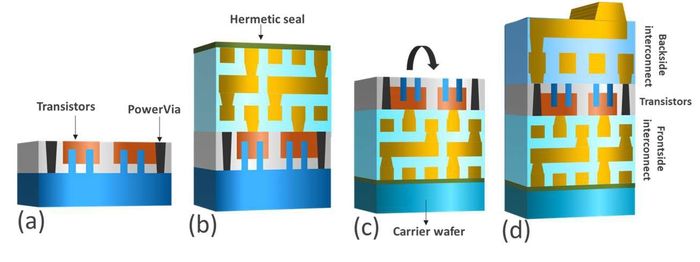

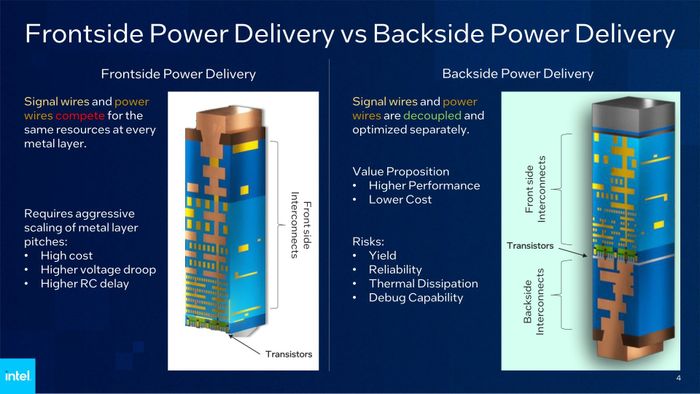

Nói một cách đơn giản, BSPDN là quá trình chuyển mạng lưới phân phối điện từ phía trước (frontside) xuống phía dưới (backside) của transistor, mở rộng không gian cho các kết nối tín hiệu (interconnect) và dây dẫn, giúp thu nhỏ transistor hơn (so với frontside).

So sánh cấu trúc phân phối điện giữa frontside và backside

Một cách dễ hiểu là bạn thi công mạng lưới phân phối điện tới từng căn hộ. Trong quá khứ, điện đến từ cột điện, sau đó đi qua các dây cáp (như mạng nhiện), đi lọt qua tường và đến đồng hồ đo (frontside); nhưng hiện nay, dây điện được đi ẩn trong tường (backside), giúp phố phường trở nên sạch sẽ hơn. Mặc dù việc này mang lại tính thẩm mỹ nhưng cũng có nhược điểm là việc sửa chữa trở nên khó khăn hơn, đôi khi phải phá tường để thực hiện sửa chữa.

Sản Xuất Đòi Hỏi Chi Phí Cao Hơn

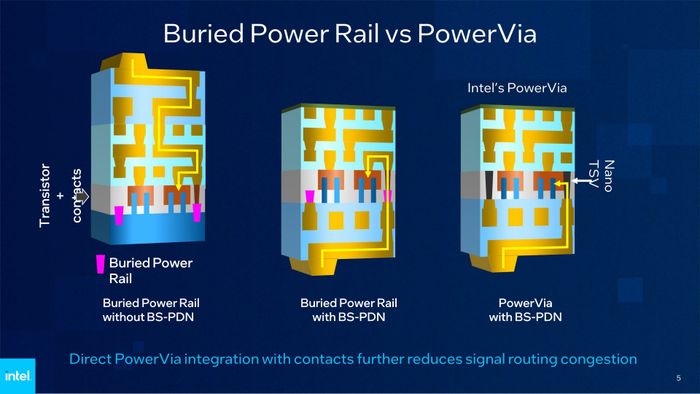

Trở lại với việc sản xuất chip bán dẫn, thực tế, BSPDN không phải là một ý tưởng mới. Trước đây, IMEC đã đưa ra ý tưởng BSPDN với tên gọi là Buried Power Rail. Còn Intel gọi công nghệ của mình là PowerVia. TSMC sử dụng cái tên Super Power Rail. Mặc dù công nghệ không mới, nhưng tại sao các hãng mới bắt đầu áp dụng? Vấn đề là BSPDN tăng gấp đôi thời gian sản xuất so với FSPDN!

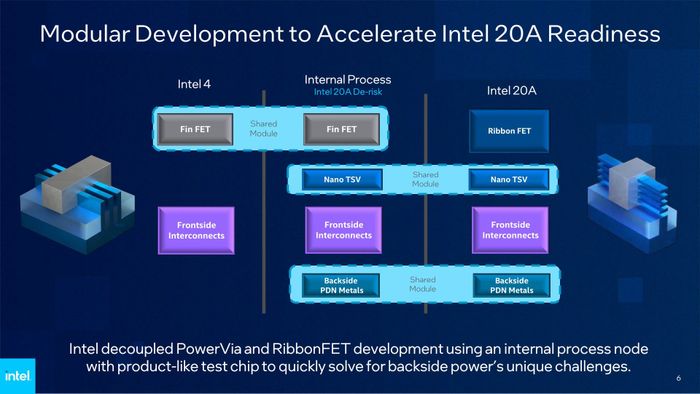

Cách Sản Xuất Transistor Kèm BSPDN của Intel

Transistor vẫn được sản xuất như thông thường nhưng mạng lưới phân phối điện (PDN) sẽ bị loại bỏ ở công đoạn này chỉ còn lại các liên kết tín hiệu. Sau khi hoàn tất phần liên kết, tấm wafer sẽ được phủ 1 lớp chặn (seal) để tách bạch nó với 1 tấm wafer khác (carrier wafer). Tấm wafer chứa các transistor ban đầu sẽ được lật úp lại, nằm đè lên carrier wafer. Phần poly-Si thừa bên dưới (backside) sẽ bị bào mòn đi, để lộ các chân tiếp điểm của transistor ra, lúc này PDN mới được thêm vào. Do tốn kém quá nhiều thời gian, BSPDN cho đến nay vẫn chưa được đưa vào sản xuất (Intel đã demo BSPDN trên Intel 4 nhưng sớm nhất phải tới Intel 20A mới áp dụng).

So Sánh Phương Pháp Buried Power Rail vs. PowerVia

Đối Mặt Với Nhiều Thách Thức Hơn

Nói về TSMC, ban đầu họ dự định áp dụng BSPDN cho node N2P (không phải N2). Nhưng tại Hội Nghị Symposium 2024 gần đây, họ đã quyết định chuyển BSPDN sang node A16. Nguyên nhân chính mặc dù không được TSMC tiết lộ, nhưng theo phân tích của các chuyên gia công nghệ, là do BSPDN thay đổi hoàn toàn cách sản xuất và thiết kế chip. Không chỉ TSMC phải điều chỉnh lại phương pháp sản xuất mà các đối tác (Apple, AMD, Qualcomm, NVIDIA...) cũng phải 'học lại' cách vẽ mạch điện (so với phương pháp cũ). Sự thay đổi đột ngột này sẽ đòi hỏi nhiều thời gian cho kỹ sư thích ứng và dẫn tới việc kéo dài quá trình thiết kế chip, gây trì hoãn trong việc ra mắt sản phẩm mới.

BSPDN Thay Đổi Cách Thiết Kế Chip Theo Cách Cơ Bản Hơn So Với Phương Pháp Trước Đây

Do đó, việc TSMC 'bỏ' BSPDN trên các node N2/N2P/N2X có thể coi là một biện pháp 'an toàn' cho cả họ lẫn khách hàng. Trong khi đó, Intel sẽ sớm áp dụng BSPDN (ở node Intel 20A), nhưng có thể nói rằng do lượng khách hàng hiện tại của Intel không nhiều, nên sự thay đổi này sẽ không ảnh hưởng nhiều tới ngành công nghiệp bán dẫn. Những con chip sử dụng PowerVia nhiều nhất sẽ là của Intel với các sản phẩm 'tự tạo'.

Nhìn chung, BSPDN hoặc PowerVia theo cách mà Intel gọi hoặc Super Power Rail theo kiểu của TSMC sẽ đánh dấu một bước tiến lớn trong lĩnh vực bán dẫn. Bằng cách 'phân chia' chi tiết mạch điện ở cả 'trên' và 'dưới' transistor sẽ giúp làm nhỏ chúng hơn nữa. TSMC cho biết node A16 sẽ có mật độ transistor cao hơn N2P từ 7~10%, tiết kiệm điện hơn 15~20% và cho phép đạt tần số cao hơn ở cùng điện áp (Vdd) từ 8~10%. Tuy nhiên, việc sản xuất lâu dài cũng đồng nghĩa với chi phí của từng con chip sẽ cao hơn. Giá của những con chip dựa trên BSPDN chắc chắn sẽ không 'rẻ mạt'...

So Sánh Node A16 vs. N2P của TSMC

Intel Sẽ Tiên Phong Áp Dụng BSPDN Trước Trên Node Intel 20A

AnandTech