Dù là những ngày nghỉ Tết âm lịch 2024, mình vẫn bận rộn với máy tính. Nảy sinh suy nghĩ về những sản phẩm công nghệ hiện đại mà chúng ta đang sử dụng, chủ yếu liên quan đến bán dẫn. Transistor không chỉ là một thành phần, mà còn là hạt nhân tạo nên rất nhiều thứ phục vụ cho cuộc sống hiện đại. Anh em có bao giờ tò mò về cách chế tạo bán dẫn chưa?

Tên và ý nghĩa

Trong bài viết này, chúng ta sẽ đụng phải nhiều thuật ngữ chuyên ngành bán dẫn. Một số quen thuộc, một số mới lạ, một số gồm những tên khác nhau, và một số có thể đồng nghĩa hoặc gần giống. Do đó, chúng ta cần một số quy định để đọc hiểu diễn ra theo cách chuẩn nhất.

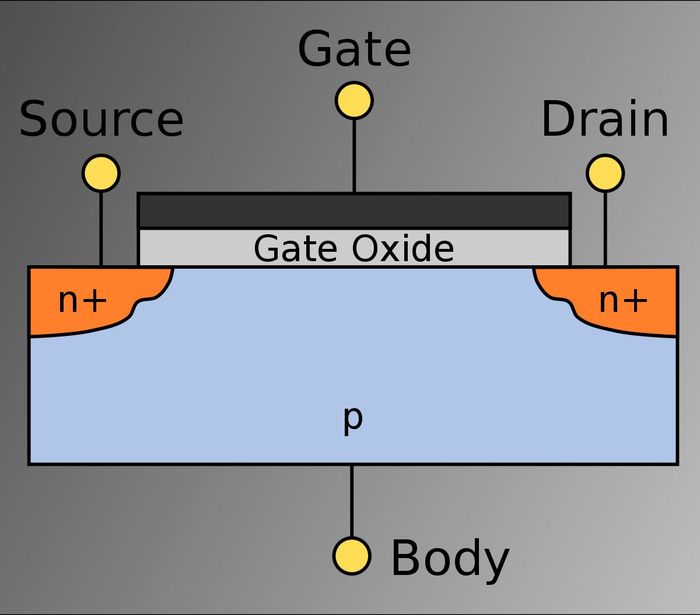

Transistor. Đây chính là khái niệm chúng ta sẽ gặp nhiều nhất và cũng là nền tảng của bài viết này. Transistor, một thiết bị bán dẫn, có nhiệm vụ kiểm soát dòng điện hoặc tăng cường tín hiệu. Các mạch điện hoặc mạch tích hợp (IC) kết hợp nhiều transistor, tạo ra những mạch điện chuyên biệt theo ý muốn của kỹ sư hoặc nhà sản xuất.

Gate hoặc cổng tín hiệu là một thành phần quan trọng của transistor. Nếu thiếu gate, transistor trở nên vô dụng - không thể kiểm soát dòng điện. Mặc dù không trực tiếp chuyển tín hiệu, gate quyết định liệu mạch điện có tín hiệu hay không. Điều này quyết định giá trị bit dữ liệu là 0 hay 1 tùy thuộc vào trạng thái của mạch điện.

Drain, nguồnKênhFET MOSFET hoặc MISFET. Đây là dạng FET được ứng dụng phổ biến nhất hiện nay. Thường được sản xuất thông qua quá trình oxy hóa lớp vỏ trên wafer silicon. Qua các phương pháp in ấn/quang học, điện phân, ăn mòn acid hoặc kết tủa kim loại... (phụ thuộc vào công nghệ bán dẫn) để tạo thành transistor. FinFET hay GAAFET cũng thuộc MOSFET, khác biệt chủ yếu ở cấu trúc các thành phần như cổng, nguồn/điện và kênh. Nói chung, MOSFET có thể hiểu là dạng FET sản xuất trên bề mặt phẳng 2D (planar), khác với không gian 3D như FinFET hay GAAFET.

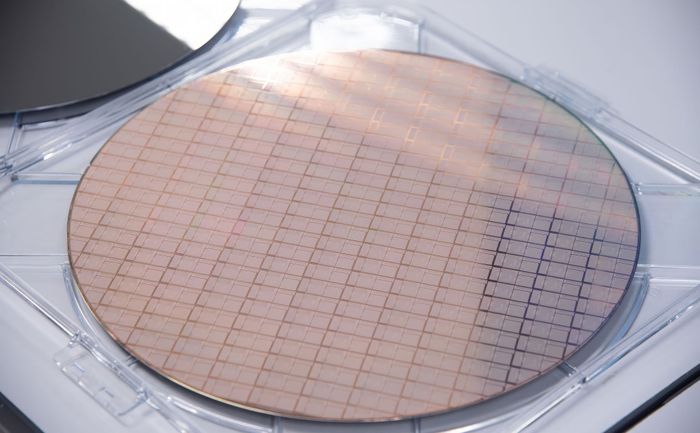

Wafer (silicon). Là nền tảng sản xuất transistor từ tinh thể silicon (Si), được tạo ra bằng cách nấu chảy cát hoặc chất chứa silic. Wafer cần độ tinh khiết cực cao tới 99.9999999% hoặc cao hơn (cấp độ 9N) để sử dụng trong việc sản xuất chip. Wafer thường có các kích thước theo đường kính như 100 mm (4 inch), 150 mm (6 inch), 200 mm (8 inch) và 300 mm (12 inch).

MOSFET hoặc MISFET. Đây là dạng FET được ứng dụng phổ biến nhất hiện nay. Thường được sản xuất thông qua quá trình oxy hóa lớp vỏ trên wafer silicon. Qua các phương pháp in ấn/quang học, điện phân, ăn mòn acid hoặc kết tủa kim loại... (phụ thuộc vào công nghệ bán dẫn) để tạo thành transistor. FinFET hay GAAFET cũng thuộc MOSFET, khác biệt chủ yếu ở cấu trúc các thành phần như cổng, nguồn/điện và kênh. Nói chung, MOSFET có thể hiểu là dạng FET sản xuất trên bề mặt phẳng 2D (planar), khác với không gian 3D như FinFET hay GAAFET.

Wafer (silicon). Là nền tảng sản xuất transistor từ tinh thể silicon (Si), được tạo ra bằng cách nấu chảy cát hoặc chất chứa silic. Wafer cần độ tinh khiết cực cao tới 99.9999999% hoặc cao hơn (cấp độ 9N) để sử dụng trong việc sản xuất chip. Wafer thường có các kích thước theo đường kính như 100 mm (4 inch), 150 mm (6 inch), 200 mm (8 inch) và 300 mm (12 inch).Tổng quan về quy trình chế tạo transistor (MOSFET)

Trước khi khám phá sâu hơn về sự khác biệt giữa 3 loại transistor ở phía trên, chúng ta cần tìm hiểu thêm về quá trình sản xuất của một transistor thông thường (planar). Trong nội dung này, chúng ta sẽ tập trung vào kỹ thuật in quang lithography, đang được ưa chuộng rộng rãi hiện nay. Mặc dù có một số sự khác biệt trong từng quy trình cụ thể hoặc từng công ty, nhưng nói chung, hầu hết đều tuân theo những bước cơ bản được mô tả dưới đây.Làm sạch waferChuẩn bị wafer. Quang chống hóa (photosuppressant). Phương pháp in quang lithography chủ yếu sử dụng các phản ứng hóa học kích thích bởi ánh sáng (photo). Những khu vực được chiếu sáng (hoặc không được chiếu sáng, tùy thuộc vào loại chất) sẽ trải qua biến đổi hóa học so với các khu vực khác. Những biến đổi này tạo điều kiện cho các phản ứng hóa học sau đó, và sau khi các phản ứng này hoàn tất, bề mặt của tấm wafer sẽ xuất hiện các cấu trúc vi mạch đa dạng, làm nền cho việc tạo ra con chip sau này.

Đối với quá trình này, việc áp dụng chất chống hóa quang là bước quan trọng nhất để kích thích các quá trình tiếp theo diễn ra. Cụ thể, tấm wafer sẽ được đặt lên một bàn xoay và chất chống hóa quang sẽ được rải lên. Nhờ vào lực ly tâm từ bàn xoay, lớp chất chống hóa quang sẽ được phân phối đều khắp nơi để đảm bảo độ đồng đều của nó trên toàn bộ wafer. Độ dày của lớp chất chống hóa quang cực kỳ quan trọng vì nó ảnh hưởng đến độ chính xác của các cấu trúc vi mạch sau này. Với các cấu trúc siêu nhỏ dưới 125 nm, độ dày tối đa cho lớp chất chống hóa quang là 0,5 µm (hoặc 500 nm). Sau đó, tấm wafer sẽ được 'nướng nhẹ' ở nhiệt độ 90 - 100 °C trong khoảng 1 phút để làm bay hơi chất chống hóa quang dư thừa trên bề mặt.

Tiếp xúc ánh sáng (hoặc chụp ánh sáng). Sau khi tấm wafer được áp dụng chất chống hóa quang, nó sẽ tiến qua bước tiếp theo - chụp ánh sáng. Đây chính là bí quyết tạo ra các transistor siêu nhỏ ở mức độ hàng trăm hoặc hàng chục nm. Điều này được thực hiện thông qua hai yếu tố chính - mặt nạ ánh sáng (photomask) và bước sóng ánh sáng (UV, DUV, EUV). Mặt nạ gồm mặt cắt bản vẽ vi mạch của chip (kích thước lớn) và một hệ thống thấu kính để thu nhỏ bản vẽ hàng trăm, thậm chí hàng ngàn lần lên tấm wafer. Tuy nhiên, để tạo ra các cấu trúc vi mạch chính xác trên tấm wafer, bước sóng ánh sáng phải càng ngắn càng tốt. Ví dụ, DUV có bước sóng từ 193 - 248 nm, còn EUV chỉ có 13,5 nm. Bước sóng càng ngắn, sai số do giao thoa ánh sáng càng thấp và 'đường vẽ' càng rõ ràng.

Quang chống hóa (photosuppressant). Phương pháp in quang lithography chủ yếu sử dụng các phản ứng hóa học kích thích bởi ánh sáng (photo). Những khu vực được chiếu sáng (hoặc không được chiếu sáng, tùy thuộc vào loại chất) sẽ trải qua biến đổi hóa học so với các khu vực khác. Những biến đổi này tạo điều kiện cho các phản ứng hóa học sau đó, và sau khi các phản ứng này hoàn tất, bề mặt của tấm wafer sẽ xuất hiện các cấu trúc vi mạch đa dạng, làm nền cho việc tạo ra con chip sau này.

Đối với quá trình này, việc áp dụng chất chống hóa quang là bước quan trọng nhất để kích thích các quá trình tiếp theo diễn ra. Cụ thể, tấm wafer sẽ được đặt lên một bàn xoay và chất chống hóa quang sẽ được rải lên. Nhờ vào lực ly tâm từ bàn xoay, lớp chất chống hóa quang sẽ được phân phối đều khắp nơi để đảm bảo độ đồng đều của nó trên toàn bộ wafer. Độ dày của lớp chất chống hóa quang cực kỳ quan trọng vì nó ảnh hưởng đến độ chính xác của các cấu trúc vi mạch sau này. Với các cấu trúc siêu nhỏ dưới 125 nm, độ dày tối đa cho lớp chất chống hóa quang là 0,5 µm (hoặc 500 nm). Sau đó, tấm wafer sẽ được 'nướng nhẹ' ở nhiệt độ 90 - 100 °C trong khoảng 1 phút để làm bay hơi chất chống hóa quang dư thừa trên bề mặt.

Tiếp xúc ánh sáng (hoặc chụp ánh sáng). Sau khi tấm wafer được áp dụng chất chống hóa quang, nó sẽ tiến qua bước tiếp theo - chụp ánh sáng. Đây chính là bí quyết tạo ra các transistor siêu nhỏ ở mức độ hàng trăm hoặc hàng chục nm. Điều này được thực hiện thông qua hai yếu tố chính - mặt nạ ánh sáng (photomask) và bước sóng ánh sáng (UV, DUV, EUV). Mặt nạ gồm mặt cắt bản vẽ vi mạch của chip (kích thước lớn) và một hệ thống thấu kính để thu nhỏ bản vẽ hàng trăm, thậm chí hàng ngàn lần lên tấm wafer. Tuy nhiên, để tạo ra các cấu trúc vi mạch chính xác trên tấm wafer, bước sóng ánh sáng phải càng ngắn càng tốt. Ví dụ, DUV có bước sóng từ 193 - 248 nm, còn EUV chỉ có 13,5 nm. Bước sóng càng ngắn, sai số do giao thoa ánh sáng càng thấp và 'đường vẽ' càng rõ ràng. Về phương pháp thực hiện, có hai loại ăn mòn - ăn mòn 'khô' bằng tia plasma hoặc ăn mòn 'ướt' bằng chất hóa học. Ăn mòn 'ướt' tương tự như tráng rửa lớp chặn quang - wafer ngâm trong một loại chất có khả năng hoà tan những vị trí có tính chất phù hợp (ví dụ, acid hoà tan base hoặc oxide) để làm lộ ra vị trí mong muốn. Còn ăn mòn 'khô' được thực hiện bằng cách bắn chùm tia plasma lên wafer qua mặt nạ quang học. Các vị trí bị bắn sẽ thay đổi tính chất và bốc hơi đi. Ăn mòn 'khô' được ưa chuộng hơn vì tốc độ mòn có thể được điều chỉnh mà không đồng đều như ăn mòn 'ướt', không gây mất mát quá nhiều vị trí không mong muốn.

Hoàn tất hoặc loại bỏ lớp chặn quang. Sau khi hoàn thành tất cả các thành phần của die chip, lớp chặn quang còn lại (chưa được rửa ở công đoạn trước) sẽ được 'gỡ bỏ' hoặc loại bỏ. Tương tự như bước ăn mòn vi mạch, lớp chặn quang có thể bị loại bỏ bằng hoá chất hoặc tia plasma. Hoá chất thay đổi thuộc tính của lớp chặn quang, làm cho nó không bám dính vào bề mặt wafer. Tia plasma chứa oxygen cũng có thể oxy hóa lớp vật liệu này một cách nhanh chóng. Những phần không mong muốn còn sót lại sẽ được xử lý tương tự.

Sản phẩm cuối cùng sẽ là tấm wafer chứa đầy die chip đã hoàn thiện. Công đoạn cuối cùng là chuyển chúng đến cơ sở cắt wafer thành từng die riêng và thực hiện kiểm tra để xác định die nào hoạt động tốt, die nào không tốt như thế nào, và chúng có thể sử dụng ở đâu. Quy trình này được gọi là harvest để tái sử dụng những die chip không hoàn hảo để tạo ra các mô hình thấp hơn để phân phối trên thị trường. Về phần này, chúng ta sẽ có một bài viết chi tiết hơn để thảo luận.

Đoạn video tóm tắt quá trình sản xuất chip.

Về phương pháp thực hiện, có hai loại ăn mòn - ăn mòn 'khô' bằng tia plasma hoặc ăn mòn 'ướt' bằng chất hóa học. Ăn mòn 'ướt' tương tự như tráng rửa lớp chặn quang - wafer ngâm trong một loại chất có khả năng hoà tan những vị trí có tính chất phù hợp (ví dụ, acid hoà tan base hoặc oxide) để làm lộ ra vị trí mong muốn. Còn ăn mòn 'khô' được thực hiện bằng cách bắn chùm tia plasma lên wafer qua mặt nạ quang học. Các vị trí bị bắn sẽ thay đổi tính chất và bốc hơi đi. Ăn mòn 'khô' được ưa chuộng hơn vì tốc độ mòn có thể được điều chỉnh mà không đồng đều như ăn mòn 'ướt', không gây mất mát quá nhiều vị trí không mong muốn.

Hoàn tất hoặc loại bỏ lớp chặn quang. Sau khi hoàn thành tất cả các thành phần của die chip, lớp chặn quang còn lại (chưa được rửa ở công đoạn trước) sẽ được 'gỡ bỏ' hoặc loại bỏ. Tương tự như bước ăn mòn vi mạch, lớp chặn quang có thể bị loại bỏ bằng hoá chất hoặc tia plasma. Hoá chất thay đổi thuộc tính của lớp chặn quang, làm cho nó không bám dính vào bề mặt wafer. Tia plasma chứa oxygen cũng có thể oxy hóa lớp vật liệu này một cách nhanh chóng. Những phần không mong muốn còn sót lại sẽ được xử lý tương tự.

Sản phẩm cuối cùng sẽ là tấm wafer chứa đầy die chip đã hoàn thiện. Công đoạn cuối cùng là chuyển chúng đến cơ sở cắt wafer thành từng die riêng và thực hiện kiểm tra để xác định die nào hoạt động tốt, die nào không tốt như thế nào, và chúng có thể sử dụng ở đâu. Quy trình này được gọi là harvest để tái sử dụng những die chip không hoàn hảo để tạo ra các mô hình thấp hơn để phân phối trên thị trường. Về phần này, chúng ta sẽ có một bài viết chi tiết hơn để thảo luận.

Đoạn video tóm tắt quá trình sản xuất chip.