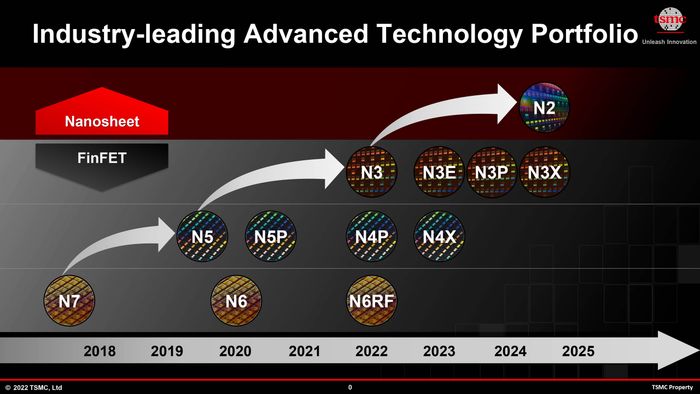

Chuyển từ các tiến trình bán dẫn 7 / 5 / 3 nm trước đó, quá trình chuyển đổi sang 2 nm (N2) của TSMC đòi hỏi thêm thời gian và chi phí với việc áp dụng kỹ thuật sản xuất nanosheet gate-all-around (GAA) hoàn toàn mới so với FinFET.Lĩnh vực chip bán dẫn là một ngành kinh doanh đa chiều và phức tạp. Không chỉ là việc các hãng gia công bán dẫn phải không ngừng cải tiến để đạt được công nghệ mới, mà còn đòi hỏi các công ty liên quan đến quá trình phát triển công nghệ, tài liệu kỹ thuật, và công cụ thiết kế chip phải thay đổi liên tục để tạo điều kiện cho sự xuất hiện của những con chip mới.Một phương pháp so sánh tương đối tiếp cận một cách dễ dàng hơn là trong lĩnh vực xây dựng, nơi chỉ có thợ hồ hoặc đốc công mà không đủ khả năng để thực hiện những công trình lớn. Để xây dựng thành công, bạn cần sự hợp tác từ cả các công ty cung cấp nguyên vật liệu, kiến trúc sư có kỹ năng và kỹ sư công trình biết cách tạo ra các tòa nhà và khắc phục sự cố khi gặp vấn đề ngoài ý muốn. Đôi khi, xây dựng nhà cũng giống như xây dựng một chip, đòi hỏi sự đồng lòng từ mọi người để mọi thứ diễn ra mượt mà.

Chuyển từ các tiến trình bán dẫn 7 / 5 / 3 nm trước đó, quá trình chuyển đổi sang 2 nm (N2) của TSMC đòi hỏi thêm thời gian và chi phí với việc áp dụng kỹ thuật sản xuất nanosheet gate-all-around (GAA) hoàn toàn mới so với FinFET.Lĩnh vực chip bán dẫn là một ngành kinh doanh đa chiều và phức tạp. Không chỉ là việc các hãng gia công bán dẫn phải không ngừng cải tiến để đạt được công nghệ mới, mà còn đòi hỏi các công ty liên quan đến quá trình phát triển công nghệ, tài liệu kỹ thuật, và công cụ thiết kế chip phải thay đổi liên tục để tạo điều kiện cho sự xuất hiện của những con chip mới.Một phương pháp so sánh tương đối tiếp cận một cách dễ dàng hơn là trong lĩnh vực xây dựng, nơi chỉ có thợ hồ hoặc đốc công mà không đủ khả năng để thực hiện những công trình lớn. Để xây dựng thành công, bạn cần sự hợp tác từ cả các công ty cung cấp nguyên vật liệu, kiến trúc sư có kỹ năng và kỹ sư công trình biết cách tạo ra các tòa nhà và khắc phục sự cố khi gặp vấn đề ngoài ý muốn. Đôi khi, xây dựng nhà cũng giống như xây dựng một chip, đòi hỏi sự đồng lòng từ mọi người để mọi thứ diễn ra mượt mà. Ngoài ra, trong lĩnh vực sản xuất chip bán dẫn, cả 'khách hàng' và các công ty 'lên đơn' để yêu cầu TSMC hoặc Samsung gia công sản phẩm đều cần 'hiểu rõ' về công nghệ bán dẫn mà họ đang đặt hàng. Điều này là bởi vì mỗi công ty có một quy trình sản xuất chip 3 nm khác nhau - transistor 3 nm của TSMC sẽ khác biệt so với của Samsung. Việc mang thiết kế chip từ quy trình 3 nm của TSMC sang Samsung và hy vọng chip cuối cùng giống nhau là không khả thi. Điều này còn không tính đến các biến thể của từng công ty, mà nếu khách hàng không hiểu rõ có thể dẫn đến việc chọn sai quy trình phù hợp cho sản phẩm của mình. Ví dụ, một con chip hiệu suất cao (thường trên 3 GHz) sẽ đòi hỏi nhiều vật liệu chuyên biệt hơn so với các con chip tiết kiệm điện.

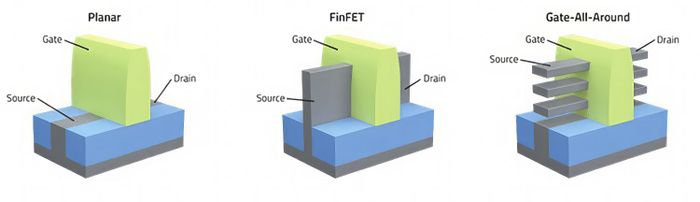

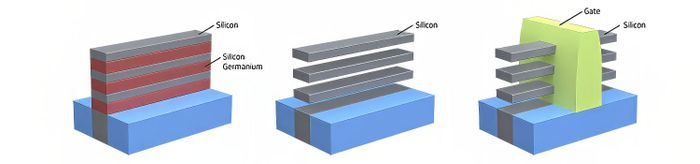

Ngoài ra, trong lĩnh vực sản xuất chip bán dẫn, cả 'khách hàng' và các công ty 'lên đơn' để yêu cầu TSMC hoặc Samsung gia công sản phẩm đều cần 'hiểu rõ' về công nghệ bán dẫn mà họ đang đặt hàng. Điều này là bởi vì mỗi công ty có một quy trình sản xuất chip 3 nm khác nhau - transistor 3 nm của TSMC sẽ khác biệt so với của Samsung. Việc mang thiết kế chip từ quy trình 3 nm của TSMC sang Samsung và hy vọng chip cuối cùng giống nhau là không khả thi. Điều này còn không tính đến các biến thể của từng công ty, mà nếu khách hàng không hiểu rõ có thể dẫn đến việc chọn sai quy trình phù hợp cho sản phẩm của mình. Ví dụ, một con chip hiệu suất cao (thường trên 3 GHz) sẽ đòi hỏi nhiều vật liệu chuyên biệt hơn so với các con chip tiết kiệm điện. Về mặt đơn giản, FinFET đã đánh dấu một bước tiến quan trọng trong thiết kế transistor khi chuyển từ kỹ thuật Planar truyền thống sang việc 'lật ngang' kênh dẫn điện (source & drain) để đạt được hiệu ứng trường (field effect) tốt hơn. Tuy nhiên, khi yêu cầu về kích thước transistor ngày càng nhỏ, FinFET cũng đang đối mặt với giới hạn của mình. GAA hoặc nanowire/nanosheet được coi là giải pháp có thể thay thế FinFET. Nói một cách tổng quan, GAA sẽ có nhiều kênh dẫn điện nằm trong cùng một cổng tín hiệu (gate) so với chỉ 1 kênh ở FinFET. Thiết kế này giúp ổn định tín hiệu FET hơn trong kích thước transistor vẫn giữ được tính nhỏ gọn. Tuy nhiên, quá trình sản xuất transistor sẽ phức tạp hơn (chúng ta sẽ có bài viết chi tiết hơn về vấn đề này). Vì vậy, tất cả các công ty liên quan đến bán dẫn sẽ phải điều chỉnh toàn bộ quy trình khi chuyển từ FinFET sang GAA.Tại sự kiện Open Innovation Platform (OIP) vừa diễn ra tại châu Âu, TSMC đã 'thông báo' rằng những người làm chip 2 nm cần sử dụng công cụ thiết kế, kiểm định, và thư viện tài nguyên mới nhất. Mặc dù có vẻ khó khăn, điều tích cực là các công cụ như EDA (Electronic Design Automation), kiểm định, IP, thậm chí là IP analog đã có sẵn trên thị trường. Dan Kochpatcharin, trưởng đơn vị quản lý thiết kế hạ tầng tại TSMC, chia sẻ: 'Với N2, chúng tôi cần bắt đầu làm việc sớm hơn 2 năm vì nanosheet khác biệt. Công cụ EDA phải sẵn sàng từ trước, vì vậy nhóm OIP phải hợp tác sớm với các đối tác. Chúng tôi đã gửi một đội ngũ lớn kỹ sư để làm việc cùng các đối tác EDA, IP và các đơn vị khác'.

Về mặt đơn giản, FinFET đã đánh dấu một bước tiến quan trọng trong thiết kế transistor khi chuyển từ kỹ thuật Planar truyền thống sang việc 'lật ngang' kênh dẫn điện (source & drain) để đạt được hiệu ứng trường (field effect) tốt hơn. Tuy nhiên, khi yêu cầu về kích thước transistor ngày càng nhỏ, FinFET cũng đang đối mặt với giới hạn của mình. GAA hoặc nanowire/nanosheet được coi là giải pháp có thể thay thế FinFET. Nói một cách tổng quan, GAA sẽ có nhiều kênh dẫn điện nằm trong cùng một cổng tín hiệu (gate) so với chỉ 1 kênh ở FinFET. Thiết kế này giúp ổn định tín hiệu FET hơn trong kích thước transistor vẫn giữ được tính nhỏ gọn. Tuy nhiên, quá trình sản xuất transistor sẽ phức tạp hơn (chúng ta sẽ có bài viết chi tiết hơn về vấn đề này). Vì vậy, tất cả các công ty liên quan đến bán dẫn sẽ phải điều chỉnh toàn bộ quy trình khi chuyển từ FinFET sang GAA.Tại sự kiện Open Innovation Platform (OIP) vừa diễn ra tại châu Âu, TSMC đã 'thông báo' rằng những người làm chip 2 nm cần sử dụng công cụ thiết kế, kiểm định, và thư viện tài nguyên mới nhất. Mặc dù có vẻ khó khăn, điều tích cực là các công cụ như EDA (Electronic Design Automation), kiểm định, IP, thậm chí là IP analog đã có sẵn trên thị trường. Dan Kochpatcharin, trưởng đơn vị quản lý thiết kế hạ tầng tại TSMC, chia sẻ: 'Với N2, chúng tôi cần bắt đầu làm việc sớm hơn 2 năm vì nanosheet khác biệt. Công cụ EDA phải sẵn sàng từ trước, vì vậy nhóm OIP phải hợp tác sớm với các đối tác. Chúng tôi đã gửi một đội ngũ lớn kỹ sư để làm việc cùng các đối tác EDA, IP và các đơn vị khác'. Đến thời điểm hiện tại, các bộ EDA lớn như Cadence, Synopsys, Ansys và Siemens đều đã được TSMC chứng nhận, cho phép các nhà thiết kế chip sử dụng chúng. Bộ EDA của Cadence và Synopsys cũng đã sẵn sàng cho việc chuyển giao thiết kế analog. Riêng bộ EDA của Cadence hỗ trợ thậm chí cả tính năng phân phối điện nền backside trong quy trình N2P.Tuy nhiên, việc phát triển thư viện IP sẽ mất nhiều thời gian hơn. Mặc dù các IP tiêu chuẩn như standard cell, GPIO/ESD, PLL, SRAM và ROM cho cả chip hiệu suất cao và di động đã sẵn sàng, nhưng các IP cho bộ nhớ non-volatile, giao diện hay chiplet vẫn chưa hoàn thiện. Điều này có thể dẫn đến trì hoãn trong quá trình thiết kế chip của một số công ty. Tuy nhiên, tổng thể, chúng sẽ sớm xuất hiện trên thị trường để đáp ứng lịch trình ra mắt tiến trình TSMC 2 nm vào năm 2025.'Phát triển IP cho transistor nanosheet không chỉ khó khăn mà còn đòi hỏi nhiều thời gian quy trình hơn. Các công ty cung cấp IP sẽ phải học lại nhiều vì nanosheet khác biệt. Chuyển từ Planar sang FinFET không chỉ khó khăn, bạn cần biết cách sản xuất FinFET. Điều tương tự khi làm nanosheet. Điều này đòi hỏi thêm thời gian học tập. Tuy nhiên, sau khi đã nắm được, mọi thứ sẽ trở nên dễ dàng. Đó là lý do chúng tôi cần bắt đầu sớm', Kochpatcharin giải thích.

Đến thời điểm hiện tại, các bộ EDA lớn như Cadence, Synopsys, Ansys và Siemens đều đã được TSMC chứng nhận, cho phép các nhà thiết kế chip sử dụng chúng. Bộ EDA của Cadence và Synopsys cũng đã sẵn sàng cho việc chuyển giao thiết kế analog. Riêng bộ EDA của Cadence hỗ trợ thậm chí cả tính năng phân phối điện nền backside trong quy trình N2P.Tuy nhiên, việc phát triển thư viện IP sẽ mất nhiều thời gian hơn. Mặc dù các IP tiêu chuẩn như standard cell, GPIO/ESD, PLL, SRAM và ROM cho cả chip hiệu suất cao và di động đã sẵn sàng, nhưng các IP cho bộ nhớ non-volatile, giao diện hay chiplet vẫn chưa hoàn thiện. Điều này có thể dẫn đến trì hoãn trong quá trình thiết kế chip của một số công ty. Tuy nhiên, tổng thể, chúng sẽ sớm xuất hiện trên thị trường để đáp ứng lịch trình ra mắt tiến trình TSMC 2 nm vào năm 2025.'Phát triển IP cho transistor nanosheet không chỉ khó khăn mà còn đòi hỏi nhiều thời gian quy trình hơn. Các công ty cung cấp IP sẽ phải học lại nhiều vì nanosheet khác biệt. Chuyển từ Planar sang FinFET không chỉ khó khăn, bạn cần biết cách sản xuất FinFET. Điều tương tự khi làm nanosheet. Điều này đòi hỏi thêm thời gian học tập. Tuy nhiên, sau khi đã nắm được, mọi thứ sẽ trở nên dễ dàng. Đó là lý do chúng tôi cần bắt đầu sớm', Kochpatcharin giải thích.